Abstract

The miniaturization of metal–oxide–semiconductor field-effect transistors (MOSFETs) has been the driving force behind the development of integrated circuits over the past 60 years; however, owing to short channel effect, reducing the gate length of MOSFETs to sub-10 nm represents a fundamental challenge. Two-dimensional materials (2DMs) with atomic scale thicknesses and non-dangling bonds interface enable sub-10 nm scale length, making them suitable candidates for advanced tech nodes beyond sub-3 nm. Although the performance metrics of a single 2DMs transistor have equalled or surpassed those of silicon, leaving no doubt about the potential of 2DMs at the laboratory level, the way of moving 2DMs from ‘lab to fab’ remains unclear. In this Review, we analyse the similarities and differences between 2DMs MOSFETs and silicon MOSFETs in the integrated circuits engineering process; we present potential solutions for channel, contact and dielectric engineering using 2DM to address the scaling challenges faced by a silicon-based device at the advanced tech node. Finally, we summarize the challenges in translating the performance of individual 2DMs devices into large-scale integrated circuits, including large-scale and stable transfer technology, high-quality material synthesis with controllable layers. Once these technical issues are properly solved, 2DMs can take full advantage of their properties at a farther scaling.

Similar content being viewed by others

Introduction

Metal–oxide–semiconductor field-effect transistors (MOSFETs) and complementary metal–oxide–semiconductor (CMOS) circuits are the cornerstone of integrated circuits and have been the driving force behind modern technological advancement1,2. For large-scale integrated circuit applications, the continuous reduction in physical size of MOSFETs enables higher overall efficiency3,4,5 through the gains in performance, power, area, cost and so on.

Device scaling informed by Moore’s law has been the primary means by which the semiconductor industry has achieved unprecedented advances in productivity and performance. Traditionally, these advances have been driven by the development of new lithographic tools, masks, photoresist materials and key-size etching processes6,7. In the early days of integrated circuit development, the efforts were focused on reducing the physical gate oxide thickness and engineering the source, drain and channel doping profile. However, owing to short channel effect (SCE), the planar scaling of the transistor faces stagnation8. Novel device architectures such as silicon-on-insulator9,10,11, fin field-effect transistors (FETs)12,13,14 and gate-all-around FETs15,16,17 have been introduced to improve the gate control capability and to suppress SCE. However, owing to the large parasitic capacitance induced by the 3D structure, the structural instability with high-aspect-ratio channel stack and the small spacing that makes high-k metal gate formation and source/drain epitaxy very difficult, the physical gate length is hard to get smaller than ~10 nm (ref. 18), below which the devices face fundamental limitations, that is, critical parts of the device cannot scale down below a few atoms in length and thickness19. At the atomic scale, strong charge scattering and quantum effects arise in a silicon transistor, making the material itself the main limitation6. Therefore, continued device scaling requires the introduction of new materials20.

Two-dimensional semiconductors are layered materials consisting of single or few layers of atoms, the atoms in the layers are held together by saturated covalent bonds and typically the thickness of the monolayer 2D materials (2DMs) is less than 1 nm (refs. 21,22). Owing to the inert and dangling-bond-free surface, the interface between different 2DMs is nearly defect-free. As a result, the charge carrier mobility in ultra-thin 2D semiconductors can be potentially very high owing to minimized lattice defects and charge scattering23,24. In addition, the phonon scattering mechanism of 2DMs also contributes to high intrinsic mobility25. Typical 2DMs, such as MoS2, WS2, WSe2, MoTe2, InSe and so on, have shown excellent electronic performance in ultra-short gate length or ultra-thin channel FETs26,27,28,29,30. Because the SCE is largely suppressed, 2DMs provide an opportunity for the continued physical scaling of transistors, making them a potential material choice for future advanced nodes31. Exploring 2DMs in prototype devices has shown much promise32,33,34 but these laboratory-scale technologies are yet to be tested in real industrial settings. Drawing on experience from silicon MOSFET technologies can provide valuable insights into ensuring 2DMs compatibility with the existing production lines towards large-scale integration (Fig. 1).

In this Review, we compare silicon-based MOSFET and 2DMs-based MOSFET technologies to reveal the key scientific issues and the corresponding performance optimization routes to achieve further scaling. On the basis of the structure of a typical transistor, we analyse the device engineering from three perspectives: channel engineering, contact engineering and dielectric engineering. In each section, we fully discuss the advantages of 2DM under ultimate scaling and promising solutions to different engineering problems. In addition, we discuss the challenges of bringing 2DMs transistor devices to large-scale integration, including the manufacturing process of MOSFET, large-scale transfer and high-quality material synthesis, in delivering the future industrialization of the advanced tech node.

Channel engineering for ultimate scaling

Dennard’s law, which has informed the scaling of integrated circuits for many decades19,35, states that the size of transistors shrinks by 30% (0.7 times) in each generation of technology, reducing their area by 50%. In terms of performance, for each technological iteration, 30% lower latency and 40% increase in operating frequency would be expected36. Moreover, to keep the electric field constant, the voltage, energy and power have to be reduced by 30%, 65% and 50%, respectively37. To keep Moore’s law going and to increase the number of devices per chip, the scaling of transistors has to follow the suit. According to the scale length theory, to improve performance and reduce power consumption, the key device parameters, such as gate length, channel thickness and oxide thickness, need to be scaled down with a uniform ratio. When applied to the planar transistor, this guiding principle has provided a long-term economically viable and resource-efficient solution for the semiconductor technology development. However, the SCE issue prevents further scaling of planar transistors.

In a traditional CMOS with a planar gate structure, the characteristic gate length for the onset of SCEs can be calculated as38:

in which tch is the thickness of a semiconducting channel, tox is the thickness of the gate dielectric and εch and εox are the dielectric constants of the channel and gate dielectric, respectively. To suppress SCE and to enhance the electrostatic gate control, fin FET and gate-all-around structures have been successively adopted. In the multigates transistor structure, the characteristic gate length can be smaller, which can be expressed as39:

This means that for the same effective gate length, the multigates structure would have better subthreshold behaviour than a planar structure. The minimum channel length could be reduced by 30% and could obtain better subthreshold characteristics. However, according to the technical path diagram of the International Roadmap for Devices and Systems (IRDS), the channel thickness in the sub-5 nm node is limited to a minimum of 6 nm (ref. 31). It can be seen that even if the structural design is adopted to reduce the SCE, the physical thickness of silicon limits the effective mobility, thus making it impossible for the device to scale further (Fig. 2a). Owing to the flat surface of the 2DM, lattice scattering is suppressed at the atomic thickness, thus maintaining high mobility at a sub-1 nm thickness. This quality represents a prominent advantage for the ultimate transistor scaling. Additionally, 2DMs are particularly suited for future potential transistor architectures such as multibridge-channel FETs and complementary FETs40,41,42,43. A typical monolayer 2D semiconductor, such as MoS2, has a low dielectric constant (~4) and a sizable bandgap (~1.8 eV), which can enhance electrostatic controllability and ensure low leakage44. Following the aforementioned equations, the characteristic gate length for 2DM transistors can be optimized to ~1–2 nm by using a thinner channel and a thinner gate dielectric layer45.

a, Silicon-based transistor scale paths. Device scaling is shifting from structural innovation to material innovation. The mismatch among channel thickness, gate length and tech node becomes more and more intense from the ~22 nm node. Since 3 nm node, channel thickness limits the scaling of the physical gate length. b, The relationship between mobility and bandgap in different 2D materials (2DMs)22,27,46,47,49,52,53,54,136,137,138,139,140. c, The radar chart comparison of N-channel metal–oxide–semiconductor (NMOS) performance between the 2DM trend and the silicon trend. The parameters represented by each edge are mobility, Vdd, leakage, gate length and Ion. The biggest advantage of 2DM lies in its ultimate physical gate length. d, The radar chart comparison of P-channel metal–oxide–semiconductor (PMOS) performance between the 2DM trend and the silicon trend. IRDS, International Roadmap for Devices and Systems.

The device mobility versus materials bandgap (Fig. 2b) provides an important metric when comparing the most promising 2DMs with silicon. MoS2 is the most studied 2D n-type semiconductor with a theoretically predicted electron mobility of 410 cm2 V−1 s−1 for a monolayer46. Provided that defects are inevitably introduced in the device fabrication process, the field-effect mobility is often degraded. Even so, the experimentally verified MoS2 electron mobility exceeds 200 cm2 V−1 s−1 at room temperature, which meets the IRDS requirements for sub-3 nm nodes22. Two-dimensional InSe has experimentally demonstrated to exhibit ultra-high electron mobility exceeding 1,000 cm2 V−1 s−1 for a few-layer InSe (three layers ~2.4 nm), but it drops sharply to 0.02 cm2 V−1 s−1 in a monolayer32,47. The mobility degradation may be related to moisture and oxygen in the environment47, and more experiments are needed to improve the performance of monolayer InSe FET. Another promising 2D semiconductor, Bi2O2Se, has a bandgap and electron mobility similar to silicon, and differs from silicon in that its performance metric is not degraded even at a monolayer thickness of 0.61 nm (ref. 48). In addition, the native oxide Bi2SeO5 can serve as a gate dielectric for Bi2O2Se, which provides a promising route for further scaling33,48,49.

As a 2D p-type semiconductor, monolayer WSe2 shows a hole mobility of more than 140 cm2 V−1 s−1, satisfying the IRDS requirement for the nodes beyond 3 nm (refs. 47,50,51,52). P-type boron phosphide has attracted attention owing to its high mobility, but the mobility degrades severely at the thickness below 3 nm (ref. 53). The synthesis of high-quality, few-layer boron phosphide films on the centimetre scale was demonstrated by the controlled pulsed laser deposition strategy54. However, for the practical application, more research is needed to solve its instability in the atmosphere55,56. Overall, 2DMs show promising results for ultimate scaling with both n-type and p-type materials, demonstrating good mobility at a channel thickness below 3 nm. Figure 2c,d compares the performance metrics of 2DM and silicon transistors, including the on-state current, off-state leakage current, mobility, gate length and operating voltage. It is worth noting that for n-type devices, the performance of 2DMs fully complies with the IRDS standard requirements. Moreover, because the gate length can reach the limit of 1 nm (refs. 57,58,59), n-type devices have the potential to be applied in sub-1 nm nodes. However, the superior performance of N-channel metal–oxide–semiconductor (NMOS) cannot compensate for the performance shortcomings of 2D P-channel metal–oxide–semiconductor (PMOS) devices. Despite its high mobility, monolayer WSe2, the on-state current does not match NMOS devices owing to the lack of appropriate metal contact engineering. Although basic CMOS functions can be achieved on a small scale by means of electrostatic regulation, contact metal work function regulation and selective growth channels, the performance of PMOS under the ultimate size is not ideal at present60,61,62,63. As a result, 2D CMOS devices with superior performance for advanced tech nodes are yet to be demonstrated. We believe that the development of PMOS should receive more attention in the future study of 2D channel engineering.

Contact engineering for ultra-thin channel

With further device miniaturization, the size of the gate, source and drain active regions of a transistor will become smaller, whereas their equivalent series resistance is expected to increase, adversely affecting the performance of the transistor64. To reduce the contact resistance, a technique has been developed in which a metal layer is deposited on the contact area, followed by a subsequent heat treatment to form a silicide, a metal silicon alloy65,66. Silicides show stable properties even upon high-temperature heat treatment after alloying, which can significantly reduce defects at the metal–silicon interface, lower the Schottky barrier and drive dopant atoms towards the interface67.

Increasing the depth of the silicide results in the reduced doping concentration at the interface between silicide and silicon, which in turn leads to a higher contact resistance. Therefore, in the manufacturing process, the depth of the silicide should not exceed half the depth of the junction. Because of the continuous scaling, both the junction depth and contact length decrease with the gate length (Fig. 3a). To maintain the drive current for optimal device operation, the doping in the source–drain area should be used to reduce the contact resistance, which means that a higher doping concentration within shallower junction depths is needed. Thus, continued reliance on the conventional source–drain structure will inevitably challenge the manufacturing process in its capability of producing doped contact regions.

a, Diagram of the relationship between the junction depth of the active region and the gate length under the silicon-based technology route. The red area represents the depth range of the junction, and the blue ball represents the depth of the silicide layer6,141. b, Two-dimensional materials contact resistance versus their contact length24,31,32,34,75,85,87,142,143,144,145,146,147. The pink areas represent P-channel field-effect transistor (P-FET) contact. The blue areas represent N-channel field-effect transistor (N-FET) contact. The green areas represent edge contact. The black ball represents the contact in advanced fin field-effect transistor (FinFET). c, Diagram of metal work functions. The metal in the red area is suitable for P-type contacts, and the metal in the blue area is suitable for N-type contacts (top). The melting temperature of the metals and the tested annealing process temperature of the transistor with the corresponding metal contact (bottom). CNT, carbon nanotube; IRDS, International Roadmap for Devices and Systems.

In a 2DMs FET, the contact between the metal and the 2D semiconductor is different from that of a silicon FET, and the depth of the 2DM contact region is ultra-shallow (<1 nm). To achieve a high performance 2DM transistor, contact engineering on ultra-thin 2DMs must be considered68. Different from the solution of silicides in bulk Si, the interface between metals and 2DMs in a top-contacted FET configuration can be formed, in most case, only via a van der Waals (vdW) gap. As such, a tunnelling barrier is introduced between the metal and the channel, suppressing charge injection, which manifests in a contact resistance several orders of magnitude higher than the theoretical quantum limit69. Therefore, much effort has been dedicated to the issue of contact resistance in 2DMs. In earlier research, metals with low work functions, such as XX, were used to form metal–semiconductor (M–S) junctions with low Schottky barriers to ensure low contact resistance70. However, experimentally this approach proved hard to realize, because of the inevitable chemical disorder and Fermi-level pinning at a typical M–S interface. For improved transistor performance, a good metal–channel interface is as important as that between the dielectric and the channel. Standard device fabrication methods often introduce additional defect-induced states, hence the Fermi-level pinning71. One effective low-energy and damage-free metal integration strategy entails transferring metals onto 2DMs, which yields a good M–S interface and de-pinning of the Fermi level72. However, the contact resistance of 2DMs MOSFETs is still much higher than that of silicon MOSFETs31.

Several studies have shown that another source of degradation of the contact resistance in 2DMs is metal-induced gap states (MIGSs)73,74. MIGSs are formed in the junction owing to the decaying metallic wavefunction with the nanometre penetration depth into the semiconductor. The corresponding solution to this is to use semimetals as M–S contacts. Semimetals are characterized by a density of states near zero at the Fermi level. If the Fermi level of the semimetal is close to the bottom of the semiconductor conduction band, the MIGS contributed by the conduction band can be substantially reduced. Bismuth is a suitable semimetal as a contact metal for MoS2, showing experimental contact resistance Rc of 123 Ω μm (ref. 34). Similarly, by using semimetal antimony (Sb) (\(01\bar{1}2\)), the contact resistance can be further reduced to 42 Ω μm, coming close to the quantum limit for a metal–2DMs contact75. Heavy doping of the contact region could result in an ohmic contact, but it is challenging to achieve in an ultra-thin 2DMs channel. Another promising approach relies on ultra-shallow contact doping technology, and the doping depth in ultra-thin 2DMs is below 1 nm (ref. 32). Through theoretical calculations, yttrium (Y) has been found to be the most suitable replacement doping metal in 2D InSe. The yttrium-doping-induced phase transition could lead to an ohmic contact InSe MOSFET and the contact resistance as low as 62 Ω μm.

In the context of scaling, the contact length decreases along with the gate length76. The contact length of silicon-based transistors has reached ~10 nm at the latest tech node31. In transistor devices, contact resistance is closely related to the contact area or contact length. In the weak-coupling limit, the contact resistance can be estimated by77,78,79

in which \({\rho }^{2{\rm{D}}}\) is the semiconductor sheet resistivity, rc is the M–S interface resistivity and Lcont is the contact length. Owing to the current crowding, the contact resistance does not depend linearly on the contact length. When the contact length is much larger than the transmission length \(\sqrt{\frac{{r}_{{\rm{c}}}}{{\rho }^{2{\rm{D}}}}}\), the contact resistance is constant and independent of the length. Therefore, to determine conclusively whether the new metal contact strategy is suitable for transistors of ultimate size, it is instrumental to study and fabricate contacts with ultra-short lengths. However, the scaling behaviour of metal–2D semiconductor contacts has been largely neglected. Most studies in contacting 2DMs report Lcont dimensions from hundreds of nanometres to a few micrometres. These advanced 2D contact works are a good demonstration of possible future contact engineering and solution strategies for 2DMs. Although excellent performance of contact resistance has been achieved (Fig. 3b), there is still room for improvement in the ultimate scaling of the contact length. In particular, edge contact could provide a path towards ultra-short contact length scaling80,81. Density functional theory calculations show that the edge contact leads to a shorter bonding distance with stronger hybridization. However, because the thickness of the 2DMs is limited to one to several atomic layers, it is technically problematic to form pure edge contacts in a large-scale circuit with the existing lithography techniques. For example, 2D edge contact and a low Rc of 670 Ω μm have been achieved on monolayer WS2 (ref. 82). Owing to its ultra-short contact length, this approach provides a possibility for the applications of 2DMs devices with ultra-short contact length.

Recently, metallic single-walled carbon nanotubes (SWCNTs) have been demonstrated to be a good contact material choice for 2DMs83,84. Owing to the perfect quasi-1D single-crystal structure, long-distance ballistic transport behaviour and high-current-carrying capacity, SWCNTs can serve as a contact with a sub-1 nm contact length. Using SWCNTs as a contact in MoS2 FETs results in the realization of the tunable Schottky barrier height85. According to the theoretical calculations, the resistance of the CNT contact can be reduced to 419 Ω μm at the ultimate contact length of 1 nm, which can be further optimized by improving the interface quality.

These approaches in advanced 2DM contact engineering have independently demonstrated their scaling potential at ultra-low contact resistance and ultra-short contact length for optimum performance (Fig. 3b). However, it is worth noting that the reported examples are mainly based on NMOS. To build high-performance CMOS, PMOS with compatible performance is essential. However, the research on high-performance PMOS is lacking. Although there are fewer suitable p-type 2DMs than n-type ones, the developed contact engineering can theoretically be extended to p-type materials. Apart from scaling, the contact of 2D PMOS requires metals with high work function86. The fundamental challenge in achieving ultra-clean p-type vdW contacts by standard electron beam evaporation on single-layer TMDs is high energy for sublimation required by high work function metals. The deposition of metal atoms onto 2D TMD layers leads to the formation of defects. For example, the formation of p-type FETs with low contact resistances of 3,300 Ω μm and 1,250 Ω μm has been obtained utilizing high work function metal and Se sacrifice layer52,87.

Finally, with the back-end-of-line thermal budget of ~400 °C in mind, the metal used for contact must have a high melting point and thermal stability because of the temperature. Some commonly used contact metals are listed in Fig. 3c, classified according to their work function and suitability for NMOS and PMOS. However, none of the existing demonstrations of ultra-low contact resistance, such as the semimetal contact (Bi, Sb (\(01\bar{1}2\))), ultra-shallow Y-doping contact, contains the verification of the device performance above the back-end-of-line temperature. Therefore, the emphasis of the 2DMs contact research should be both on contact resistance and on thermal stability.

Dielectric engineering for 2DM–insulator interface

The insulating dielectric layer, bridging the gate and the channel, is implemented to prevent leakage and transmit the gate electric field. Surface conductive channel between the source and drain electrodes is generated under the control of this electric field. The physical properties of the channel material, such as conductivity, carrier mobility and impurity concentration, have a direct impact on the current transfer efficiency and the switching speed of the MOSFET. Additionally, the quality of the dielectric and the interface affects the controllability of the gate to the channel, which in turn affects key parameters such as the threshold voltage of the MOSFET, subthreshold slope and leakage current. Therefore, the performance of a MOSFET depends not only on the characteristics of the channel material but also on the quality of the gate insulator interface and the overall performance of the gate insulator.

In particular, the excellent interface of Si–SiO2 is one of the main reasons why silicon has become the material of choice in the semiconductor technology (Fig. 4a). The number of silicon dangling bonds at the interface can be reduced to the levels below 1010 cm−2 via gas passivation88,89. Apart from Si–SiO2, there has been a glaring lack of suitable insulating materials, which limits other channel materials from entering the mass market. Similarly, finding a suitable insulator for 2DMs is a big challenge because of their inert surface that provides no nucleation sites. For this reason, the standard oxides deposition techniques cannot be used for 2DMs channels owing to the formation of multiple defects at the 2DM–oxide interface90,91 (Fig. 4b). Growing oxide films directly by atomic layered deposition (ALD) results in uneven structures that cannot completely cover the surface, which leads to at least two kinds of defects: the interface and dielectric defects. Although these defects can be reduced by various annealing steps, their density is still much higher than that at the ideal Si–SiO2 interface. To fully exploit the advantages of 2DMs, it is crucial to develop effective strategies to improve the quality of the 2DMs–insulator interface (Fig. 4c). One strategy is to construct a fully 2D vdW-stacked gate dielectric (Fig. 4c, left). As the layers of different 2DMs are connected by vdW forces, the interface traps and defects between the channel and the insulator can be greatly reduced, thus achieving good dielectric extension92. The second strategy relies on a seeding layer between the 2D channel and the bulk insulator. For example, a seeding layer can be introduced as a medium for the oxide during ALD growth (Fig. 4c, middle). Another approach is via partial oxidation of few layers of 2DMs and their transformation into native oxides, which maintains the vdW heterostructure between the channel and the oxide (Fig. 4c, right). This process can potentially lead to atomically abrupt and defect-free interfaces, as promising as the Si–SiO2 interface.

a, Typical bulk silicon oxide dielectric integration. The silicon and the oxide are connected by covalent bonds. b, The two kinds of defects when the conventional atomic layered deposition method is used to directly grow the insulation layer on the surface of 2D materials (2DMs): the interface defects and the dielectric defects. c, Schematic diagram of the effective strategies for the integration of dielectrics on 2DMs, including van der Waals (vdW) stack dielectric, seed-layer inducing strategy and in situ oxidation. d, The quality of the dielectric under several different strategies is summarized, the ball represents the density of the interface state and the column represents the gate leakage current33,95,96,98,99,100,148. e, Diagram of the relationship between dielectric constant and bandgap value of different dielectrics. The black colour block represents the traditional bulk material oxide dielectric, and the colourful blocks are the dielectrics that have verified the integration with 2DMs149,150. hBN, hexagonal boron nitride; PTCDA, 3,4,9,10-perylene-tetracarboxylic dianhydride.

Although the aforementioned technical paths can, in principle, achieve good 2D interfaces, the feasibility of different strategies needs proper engineering evaluation. As far as the interface and dielectric defects are concerned, we use two parameters: density of the interface states (Dit) and gate leakage current density to evaluate the three aforementioned strategies. The continuous power scaling requires a device to operate at the lowest possible voltage. To this end, subthreshold swing (SS) has to be small to keep the device in the on state in a low voltage range. The SS of the device is directly related to the interface quality between the insulator and the channel, which can be described as91:

in which Cchannel and Cinsulator are capacitances of the channel and the insulator of the dielectric, respectively. The smaller the density of the interface states Dit, the closer the SS of the device to the ideal value of 60 mV per decade at room temperature. For Dit over 1010 cm−2 eV−1, the SS requirement for power scaling cannot be perfectly met.

Aggressive scaling of the gate insulator increases direct tunnelling and thus results in large leakage currents even at low voltages. In addition to direct tunnelling through the insulator, the Fowler–Nordheim tunnelling through the bent barrier and trap-assisted tunnelling, which becomes dominant at high defect density, are all performance-limiting factors to consider93.

On the basis of the existing literature, we compare the performance metrics in three different technological paths (Fig. 4d). The seed-layer-inducing strategy provides closely distributed sites for ALD nucleation, the method of constructing a seed layer including oxidized metal layers, organic molecules, plasma treatment and so on. However, all these approaches are not without drawbacks. For example, widely used metal oxidation processes are affected by the inherent roughness of evaporating metal films as well as by the destruction of high-energy metal ions, which leads to a threshold voltage drift94. Plasma and ozone surface treatments involve energetic and reactive substances, which can also introduce defects and interface states. Using 3,4,9,10-perylene-tetracarboxylic dianhydride has been proposed as the molecular seeding layers95. Ultra-thin equivalent oxide thickness (EOT) and good dielectric performance can be achieved on a single device, but because the intrinsic dielectric constant of 3,4,9,10-perylene-tetracarboxylic dianhydride is not high, there is still room for improvement in achieving thinner EOT. Additionally, owing to these layers being formed by discrete molecules, the large-scale homogeneous film integration may be challenging. More recently, a kind of inorganic molecular crystal Sb2O3 has been tested as the compatible oxide seeding layer between 2D MoS2 and high-κ HfO2 (ref. 42). By means of thermal evaporation, an ultra-thin (1 nm) Sb2O3 buffer layer is uniformly grown on the surface of the 2DMs at a slow speed. Using this strategy, a good semiconductor-to-insulator interface can be formed providing a hydrophilic surface for the deposition of the high-κ dielectric. This type of a seed layer is a promising candidate for the combination of 2DMs and high-κ dielectric. However, it needs to be experimentally verified in small-footprints devices and large-scale circuits. Another strategy of in situ oxidation, which is the partial oxidation of specific 2DMs with the same heterostructure, is also a promising solution for high-quality 2D dielectric engineering for large-scale integration. A relatively new material Bi2O2Se with its Bi2SeO5 native oxide is one representative system. The most notable point apart from the superior quality of the dielectric Bi2SeO5 has a high κ constant (~21), which makes it ideal for the scaling of transistors with small equivalent oxide layer thickness33,49.

All the aforementioned strategies increase the chances of dielectric integration, but Dit remains much higher than that of the Si–SiO2 interface. Therefore, as the molecular structure of 2DMs is intrinsically different from silicon, we believe that the most potent dielectric engineering strategy is via vdW bonding. Applying 2D crystalline insulators such as hexagonal boron nitride (hBN) to stack vdW dielectric is a promising solution for 2D devices. As an inert and dangling bond-free 2D insulator, hBN has been used as an excellent encapsulation of 2D devices to improve their mobility. Using post-annealing of an MoS2 channel sandwiched between hBN gate dielectric layers, excellent switching characteristics have been observed with SS of 63 mV per decade and Dit of 5 × 109 cm−2 eV−1, on par with silicon technology standards96. However, hBN has low dielectric constant (~6) and its bandgap (~6 eV) in bulk is not ideal, which leads to high leakage current at ultra-thin EOT97. Therefore, it is difficult to envisage the use of hBN in advanced technology nodes that require ultra-thin insulator thickness. Thus, the defect-free ionic crystal insulators, such as CaF2 and SrTiO3, have been considered as an alternative to hBN98,99. Compared with hBN, these ionic crystals have a higher dielectric constant for further scaling; however, the density of states is significantly increased at the same time, which results in a decrease of the gate capacitance and an increase in the leakage current. Recently, a dry dielectric integration strategy compatible with large areas of 2D devices has been reported100. By using polyvinyl alcohol as a sacrificial layer, ultra-thin Al2O3 and HfO2 of sub-3 nm thickness can be pre-deposited and then mechanically dry-released and dry-laminated onto wafer-scale monolayer MoS2. The 2DMs–insulator interface achieved in this way is different from that obtained by the ALD method. In particular, owing to a weakly coupled vdW dielectric interface, Dit is reduced to 7.6 × 109 cm−2 eV−1, which is comparable with the Si–SiO2 interface. As the dry-transfer process of the dielectric is universal, more bulk materials of high-κ oxide dielectric are expected to be integrated into 2D devices. However, the dielectric layer integration in this strategy is achieved by transfer, which is challenging for high-density integration. The oxide insulators suitable for using as dielectric layer are listed in Fig. 4e. In general, to obtain thinner EOT and smaller leakage, it is necessary to consider a tradeoff between the κ constant and bandgap. As a general rule, most good oxide dielectric materials have a bandgap between 4 eV and 8 eV.

Overall, the existing examples of 2DMs dielectric engineering have proved potent in forming high-quality interfaces, but more systematic optimization schemes are required to explore the validity of these strategies for large-scale transistor circuits. Among the proposed approaches, the use of vdW stack dielectric enables the best interface, but, once again, achieving high-density device integration presents a serious challenge. To this end, seed-layer inducing and in situ oxidation methods have potential to support high-density device integration, but the interface quality has to be improved.

The challenges of bringing 2DMs transistor devices to large-scale integration

Table 1 summarizes the benchmarks of different device engineering technologies from the compatibility to large-scale integration. As mentioned earlier, despite the solid performance of n-type 2DMs MOSFETs, the demonstration of high-performance p-type 2DMs MOSFETs is still lacking. Therefore, going from a single device demonstration to large-scale integration is not a straightforward process. The ultra-thin body and inert surface of the 2DMs makes it impossible to directly integrate them into silicon MOSFETs manufacturing technology. Although the semimetal contact technology and the ultra-shallow doping of a contact region strategy have yielded low contact resistance at a long contact length, the demonstration of good thermal stability of these new technologies is still lacking. Another major challenge is the quality of the 2DM–insulator interface, which needs to be improved to support high-density device integration.

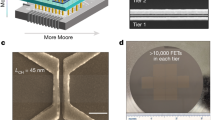

To achieve large-scale integration, the entire front-end process for circuits must be taken into consideration. To this end, it is worthwhile to compare the fabrication process of silicon-based and 2DMs-based large-scale circuits (Fig. 5).

a, Schematic diagram of the typical silicon-based device integration process. The channel is doped by ion implantation, then the gate is defined by atomic layered deposition and polycrystalline silicon mask etching and, finally, self-aligned contact area doping and metallization are achieved. b, Schematic diagram of the 2D material (2DM)-based device integration process. Large-scale 2DM channel material growth, the channel is then defined by etching and metallization, the gate dielectric is grown and, finally, the gate electrode is deposited.

Self-aligned gates are used to fabricate transistors in silicon-based semiconductor processes and are still used in most modern integrated circuits101,102. In the silicon front-end process flow, the relative positions of the gate and source–drain electrodes are defined by the self-aligned process (Fig. 5a). The gate dielectric layer is formed at the beginning of the process and the patterned gate is then deposited on it. The source–drain region is then doped; in the case of polysilicon gate, the gate is doped at the same time. After the doping of the source–drain region, the edge of the doping region defines the channel. The defined channel is always placed perfectly under the control gate, which greatly reduces the parasitic capacitance.

In the 2DMs-based front-end process flow (Fig. 5b), the source and drain electrode regions are defined first, then the dielectric oxide is grown or transferred onto the 2DM channel and electrodes. Finally, a gate electrode is formed on the oxide layer. In this process, to ensure the ability of the gate to control the entire channel, a considerable overlap region is formed between the gate region and the source–drain region. This results in a large parasitic capacitance between the gate and source–drain regions and increases the gate leakage current. According to the Miller effect, the greater the parasitic capacitance Cgd, the lower the switching speed103,104. Although some researchers have studied the self-aligned process of 2DMs, the performance of oxides integrated in this way needs to be further improved to meet the requirements of IRDS for sub-3 nm nodes105,106.

Different from the silicon-integrated process, the synthesized 2DMs films are usually transferred to a target substrate. Therefore, the stable synthesis and transfer of wafer-level 2DMs film should also be considered for commercialization of 2DM technology43,47,54,99,107,108,109,110,111,112,113,114,115,116,117,118,119,120,121,122,123,124,125 (Fig. 6a).

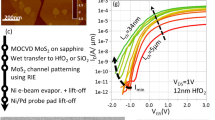

Chemical vapour deposition (CVD) is a powerful approach to synthesize 2DMs films on a range of substrates that has been used to grow large-area 2DMs films with controllable thicknesses. Graphene, MoS2, MoSe2, WS2, WSe2, Bi2O2Se and hBN films have been successfully grown through well-designed CVD systems at wafer scale99,112,126,127,128,129,130,131. At present, CVD technique enables the growth of single-crystal monolayer films as opposed to earlier demonstration of polycrystalline 2DMs. Recently, the highest room temperature mobility of 232.7 cm2 V–1 s–1 in a 4-inch CVD MoS2 has been reported, showing the feasibility of large-area films with high mobility123. An improved CVD synthesis method has been reported that involves a controlled release of precursors and substrates pre-deposited with amorphous Al2O3 to ensure uniform synthesis of monolayer MoS2 as large as 12 inch, suitable for commercialization124. The semiconductor industry has been exploring the compatibility of 2DMs with back-end-of-line processes, which practically limits the growth temperature of 2D flakes to that below 450 °C. ALD is a versatile tool suitable for low temperatures. Moreover, because the growth can be controlled at an atomic layer thickness, and the reaction is self-limited to the surface of the substrate, it is, theoretically at least, suitable for the synthesis of 2DMs132. At present, only a handful of 2D flakes synthesized by direct growth can meet the IRDS requirements for channel mobility (Fig. 6b).

In small-scale laboratory settings, high-quality 2DM films are still obtained via mechanical exfoliation, which yields random thicknesses and small flake size. Hence, there has been significant motivation to adapt the conventional mechanical exfoliation method to a larger scale. One alternative approach has been to introduce a metal (for example, Au) or polymeric intermediate substrate to improve the exfoliation yield and lateral size of 2D flakes133. With this method, a few millimetre uniform and high-quality 2D flakes can be obtained, which could be used in small-scale circuit function verification. The liquid-phase exfoliation is another well-established laboratory-scale method to obtain 2DMs. However, these methods are not fit for large-scale integrated circuits.

Transferring 2D films onto desired substrates is a key step for the integration of 2DM. Depending on whether chemical solvents are used in the transfer process, they can be broadly divided into two categories: dry transfer and wet transfer. For dry transfer, the usual process involves stripping of a 2DM from its substrate onto an organics stamp (usually polydimethylsiloxane) and then, with the use of a microscope, affixing the stamp with the adhered 2DM to a target substrate. Finally, a heat treatment is used to remove the stamp from the substrate, thus completing the transfer. Dry transfer technique is suitable for most 2DMs and avoids the introduction of unwanted contaminants as the process does not rely on chemical solvents. However, limited by the adhesion between the organic stamps and the 2DMs, the sample size of the transferred flakes does not exceed several centimetres. To this end, a modified dry transfer method has been proposed100. The method proceeds through the following steps: first, an organic sacrificial layer is covered on the original substrate, then insulator is pre-deposited on the sacrificial layer and finally the insulator is mechanically dry-released from the original substrate and laminated on the top of wafer-scale MoS2 through the sacrificial layer. Through this approach, 2-inch 2DM-compatible dry dielectric transfer can be achieved, enabling 2DM dielectric integration.

Wet transfer is usually used in conjunction with CVD technology. 2DMs obtained via CVD are typically grown on metal substrates or foils; therefore, they tend to adhere more strongly to the original substrate, a peel-off step hard to perform. Wet transfer involves spin-coating of an organic layer onto 2DM grown on a metal substrate. Then, the substrate is etched with a chemical solution and dried to obtain an organic support layer in contact with the 2DMs film. Finally, the 2DM film is transferred onto the target substrate following the same method as dry transfer. Compared with dry transfer, wet transfer is more suitable for large-area film transfer of 2DMs because the strength of adhesion of the substrate to the 2DMs is not a consideration. However, because chemical solvents are introduced in the transfer process, it is likely to lead to film breaking, wrinkling and bending. Owing to the different wettability of 2DM films and the growth substrates, 2DM films can be easily and quickly delaminated by deionized water at room temperature. As a result, an improved wet transfer method has been reported showing good transfer at a 6-inch size134. Drawing on the principle of wet transfer, a metal-assisted transfer approach has also been recently proposed, which is well suited for basic device performance verification in the laboratory owing to the ability to consistently obtain high-quality monolayer 2DMs133. In particular, wet transfer technology has been proposed based on wafer-bonding machines for large-scale semiconductor manufacturing lines135. The study claims to have successfully transferred monolayer WS2 and some other 2DMs between 300 mm wafers by utilizing bisbenzocyclobutene as an adhesive sacrificial layer, which could prove promising if extended to other 2DMs. In principle, both dry and wet transfer methods can be used for wafer-scale 2DM transfer. More commercial equipment and technical methods need to be developed to improve transfer efficiency. Finally, the material synthesis and transfer techniques are summarized in Table 2. To accelerate the ‘lab-to-fab’ transition of 2DMs, work on large-scale growth and wafer-scale transfer processes should be intensified.

Outlook

Owing to high performance at atomic thicknesses, 2DMs open up the possibility of further transistor miniaturization beyond the limits of bulk materials. Building upon the extensive experience of the continued innovation in silicon MOSFET technology and through the optimization and further development of channel, contact and dielectric engineering approaches, 2DMs could deliver a breakthrough in the device performance at the ultimate scale. For that, the optimization of 2D transistors has to be approached holistically, by considering different types of device engineering. As far as the overall front-end process is concerned, the self-aligned integration process, high-quality wafer-scale 2DMs synthesis and transfer should be completed.

References

Bardeen, J. & Brattain, W. H. The transistor, a semi-conductor triode. Phys. Rev. 74, 230 (1948).

Atalla, M. M., Tannenbaum, E. & Scheibner, E. Stabilization of silicon surfaces by thermally grown oxides. Bell Syst. Tech. J. 38, 749–783 (1959).

Kilby, J. S. Invention of the integrated circuit. IEEE Trans. Electron Devices 23, 648–654 (1976).

Chang, L. et al. Extremely scaled silicon nano-CMOS devices. Proc. IEEE 91, 1860–1873 (2003).

Cheng, Z. et al. How to report and benchmark emerging field-effect transistors. Nat. Electron. 5, 416–423 (2022). This study is a reference value for the benchmark of 2DM-based transistors.

Plummer, J. D. & Griffin, P. B. Material and process limits in silicon VLSI technology. Proc. IEEE 89, 240–258 (2001).

Ito, T. & Okazaki, S. Pushing the limits of lithography. Nature 406, 1027–1031 (2000).

Auth, C. et al. A 10 nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, self-aligned quad patterning, contact over active gate and cobalt local interconnects (IEEE, 2017).

Celler, G. K. & Cristoloveanu, S. Frontiers of silicon-on-insulator. J. Appl. Phys. 93, 4955–4978 (2003).

Cristoloveanu, S. Silicon on insulator technologies and devices: from present to future. Solid State Electron. 45, 1403–1411 (2001).

Colinge, J.-P. Silicon-on-Insulator Technology: Materials to VLSI (Springer, 2004).

Krivokapic, Z. et al. 14nm Ferroelectric FinFET technology with steep subthreshold slope for ultra low power applications (IEEE, 2017).

Lee, H. J. et al. Intel 22 nm FinFET (22FFL) process technology for RF and mm wave applications and circuit design optimization for FinFET technology (IEEE, 2018).

Bin, Y. et al. FinFET scaling to 10 nm gate length (IEEE, 2002).

Loubet, N. et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET (IEEE, 2017).

Singh, N. et al. High-performance fully depleted silicon nanowire (diameter/spl les/5 nm) gate-all-around CMOS devices. IEEE Electron Device Lett. 27, 383–386 (2006).

Bae, G. et al. 3 nm GAA technology featuring multi-bridge-channel FET for low power and high performance applications (IEEE, 2018).

He, X. et al. Impact of aggressive fin width scaling on FinFET device characteristics (IEEE, 2017).

Dennard, R. H. et al. Design of ion-implanted MOSFET’s with very small physical dimensions. IEEE J. Solid-State Circuits 9, 256–268 (1974).

Vogel, E. Technology and metrology of new electronic materials and devices. Nat. Nanotechnol. 2, 25–32 (2007).

Wang, Q. H., Kalantar-Zadeh, K., Kis, A., Coleman, J. N. & Strano, M. S. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. Nat. Nanotechnol. 7, 699–712 (2012).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Liu, Y., Duan, X., Huang, Y. & Duan, X. Two-dimensional transistors beyond graphene and TMDCs. Chem. Soc. Rev. 47, 6388–6409 (2018).

English, C. D., Shine, G., Dorgan, V. E., Saraswat, K. C. & Pop, E. Improved contacts to MoS2 transistors by ultra-high vacuum metal deposition. Nano Lett. 16, 3824–3830 (2016).

Cheng, L. & Liu, Y. What limits the intrinsic mobility of electrons and holes in two dimensional metal dichalcogenides? J. Am. Chem. Soc. 140, 17895–17900 (2018).

Li, H. et al. From bulk to monolayer MoS2: evolution of Raman scattering. Adv. Funct. Mater. 22, 1385–1390 (2012).

Bandurin, D. A. et al. High electron mobility, quantum Hall effect and anomalous optical response in atomically thin InSe. Nat. Nanotechnol. 12, 223–227 (2017).

Zhao, W. et al. Evolution of electronic structure in atomically thin sheets of WS2 and WSe2. ACS Nano 7, 791–797 (2013).

Ruppert, C., Aslan, B. & Heinz, T. F. Optical properties and band gap of single- and few-layer MoTe2 crystals. Nano Lett. 14, 6231–6236 (2014).

Li, H., Wu, J., Yin, Z. & Zhang, H. Preparation and applications of mechanically exfoliated single-layer and multilayer MoS2 and WSe2 nanosheets. Acc. Chem. Res. 47, 1067–1075 (2014).

International Roadmap for Devices and Systems. International Roadmap for Devices and Systems: 2022 update (IEEE, 2022).

Jiang, J., Xu, L., Qiu, C. & Peng, L.-M. Ballistic two-dimensional InSe transistors. Nature 616, 470–475 (2023).

Tan, C. et al. 2D fin field-effect transistors integrated with epitaxial high-k gate oxide. Nature 616, 66–72 (2023). This study demonstrates 2DMs compatibility for FinFET structures.

Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021). This study demonstrates a promising contact strategy between 2DMs and semimetal.

Frank, D. J. et al. Device scaling limits of Si MOSFETs and their application dependencies. Proc. IEEE 89, 259–288 (2001).

Davari, B., Dennard, R. H. & Shahidi, G. G. CMOS scaling for high performance and low power — the next ten years. Proc. IEEE 83, 595–606 (1995).

De, V. & Borkar, S. Technology and design challenges for low power and high performance (ACM, 1999).

Yan, R. H., Ourmazd, A. & Lee, K. F. Scaling the Si MOSFET: from bulk to SOI to bulk. IEEE Trans. Electron Devices 39, 1704–1710 (1992).

Suzuki, K., Tanaka, T., Tosaka, Y., Horie, H. & Arimoto, Y. Scaling theory for double-gate SOI MOSFET’s. IEEE Trans. Electron Devices 40, 2326–2329 (1993).

Huang, X. et al. High drive and low leakage current MBC FET with channel thickness 1.2 nm/0.6 nm (IEEE, 2020). Multibridge-channel MOSFET achieved by taking full advantage of the 2DMs structure.

Liu, Y. et al. A quantum corrected compact model of experimentally fabricated GAA 2-D MBCFETs. IEEE Trans. Electron Devices 70, 891–898 (2023).

Tong, L. et al. Heterogeneous complementary field-effect transistors based on silicon and molybdenum disulfide. Nat. Electron. 6, 37–44 (2023). Complementary FET structure realized by combining 2DMs and silicon, demonstrating the compatibility of the 2DM with the existing semiconductor technologies.

Xiong, X. et al. Demonstration of vertically-stacked CVD monolayer channels: MoS2 nanosheets GAA-FET with ion > 700 µA/µm and MoS2/WSe2 CFET (IEEE, 2021).

Conley, H. J. et al. Bandgap engineering of strained monolayer and bilayer MoS2. Nano Lett. 13, 3626–3630 (2013).

Nourbakhsh, A. et al. MoS2 field-effect transistor with sub-10 nm channel length. Nano Lett. 16, 7798–7806 (2016).

Kaasbjerg, K., Thygesen, K. S. & Jacobsen, K. W. Phonon-limited mobility in n-type single-layer MoS2 from first principles. Phys. Rev. B 85, 115317 (2012).

Feng, W., Zheng, W., Gao, F. & Hu, P. Atomically thin InSe: a high mobility two-dimensional material. Sci. China Technol. Sci. 60, 1121–1122 (2017).

Zhou, X. et al. Step-climbing epitaxy of layered materials with giant out-of-plane lattice mismatch. Adv. Mater. 34, 2202754 (2022).

Li, T. et al. A native oxide high-κ gate dielectric for two-dimensional electronics. Nat. Electron. 3, 473–478 (2020). This study shows a dielectric growth of 2DMs by in situ oxidation, promising as a dielectric integration process for large-scale 2DM transistor circuits.

Ji, H. G. et al. Chemically tuned p- and n-type WSe2 monolayers with high carrier mobility for advanced electronics. Adv. Mater. 31, 1903613 (2019).

Chen, P. et al. Anisotropic carrier mobility from 2H WSe2. Adv. Mater. 34, 2108615 (2022).

Kwon, G. et al. Interaction- and defect-free van der Waals contacts between metals and two-dimensional semiconductors. Nat. Electron. 5, 241–247 (2022).

Li, L. et al. Black phosphorus field-effect transistors. Nat. Nanotechnol. 9, 372–377 (2014).

Wu, Z. et al. Large-scale growth of few-layer two-dimensional black phosphorus. Nat. Mater. 20, 1203–1209 (2021). This study demonstrates the large-scale growth of P-type 2DMs.

Sui, Y. et al. Recent advances in black-phosphorus-based materials for electrochemical energy storage. Mater. Today 42, 117–136 (2021).

Li, Q. et al. Recent advances in black phosphorus-based electrochemical sensors: a review. Anal. Chim. Acta 1170, 338480 (2021).

Wu, F. et al. Vertical MoS2 transistors with sub-1-nm gate lengths. Nature 603, 259–264 (2022).

Liu, L. et al. Transferred van der Waals metal electrodes for sub-1-nm MoS2 vertical transistors. Nat. Electron. 4, 342–347 (2021).

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354, 99–102 (2016). This study discusses ultimate 1 nm physical gate length transistors.

Baugher, B. W. H., Churchill, H. O. H., Yang, Y. & Jarillo-Herrero, P. Optoelectronic devices based on electrically tunable p–n diodes in a monolayer dichalcogenide. Nat. Nanotechnol. 9, 262–267 (2014).

Brien, K. P. O. et al. Advancing 2D monolayer CMOS through contact, channel and interface engineering (IEEE, 2021).

Chiu, M.-H. et al. Metal-guided selective growth of 2D materials: demonstration of a bottom-up CMOS inverter. Adv. Mater. 31, 1900861 (2019).

Nipane, A., Karmakar, D., Kaushik, N., Karande, S. & Lodha, S. Few-layer MoS2 p-type devices enabled by selective doping using low energy phosphorus implantation. ACS Nano 10, 2128–2137 (2016).

Pop, E., Sinha, S. & Goodson, K. E. Heat generation and transport in nanometer-scale transistors. Proc. IEEE 94, 1587–1601 (2006).

Kim, G., Shin, H., Lee, J. & Lee, W. A review on silicide-based materials: thermoelectric and mechanical properties. Met. Mater. Int. 27, 2205–2219 (2021).

Murarka, S. P. Silicide thin films and their applications in microelectronics. Intermetallics 3, 173–186 (1995).

Lee, Y. J. et al. Low-temperature microwave annealing processes for future IC fabrication — a review. IEEE Trans. Electron Devices 61, 651–665 (2014).

Schulman, D. S., Arnold, A. J. & Das, S. Contact engineering for 2D materials and devices. Chem. Soc. Rev. 47, 3037–3058 (2018).

Cui, X. et al. Low-temperature ohmic contact to monolayer MoS2 by van der Waals bonded Co/h-BN electrodes. Nano Lett. 17, 4781–4786 (2017).

Das, S., Chen, H.-Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett. 13, 100–105 (2013).

Ngo, T. D. et al. Fermi-level pinning free high-performance 2D CMOS inverter fabricated with van der Waals bottom contacts. Adv. Electron. Mater. 7, 2001212 (2021).

Liu, Y. et al. Approaching the Schottky–Mott limit in van der Waals metal–semiconductor junctions. Nature 557, 696–700 (2018). This study provides ohmic contact of 2DM–metal by the transfer process.

Nishimura, T., Kita, K. & Toriumi, A. Evidence for strong fermi-level pinning due to metal-induced gap states at metal/germanium interface. Appl. Phys. Lett. 91, 123123 (2007).

Sotthewes, K. et al. Universal Fermi-level pinning in transition-metal dichalcogenides. J. Phys. Chem. C 123, 5411–5420 (2019).

Li, W. et al. Approaching the quantum limit in two-dimensional semiconductor contacts. Nature 613, 274–279 (2023). One of the best-performing 2DM transistors ever reported, approaching device requirements of IRDS sub-3 nm nodes.

Wei, T. et al. Two dimensional semiconducting materials for ultimately scaled transistors. iScience 25, 105160 (2022).

Berger, H. H. Models for contacts to planar devices. Solid State Electron. 15, 145–158 (1972).

Scott, D. B., Hunter, W. R. & Shichijo, H. A transmission line model for silicided diffusions: impact on the performance of VLSI circuits. IEEE J. Solid-State Circuits 17, 281–291 (1982).

Allain, A., Kang, J., Banerjee, K. & Kis, A. Electrical contacts to two-dimensional semiconductors. Nat. Mater. 14, 1195–1205 (2015).

Wang, L. et al. One-dimensional electrical contact to a two-dimensional material. Science 342, 614–617 (2013).

Cheng, Z. et al. Immunity to contact scaling in MoS2 transistors using in situ edge contacts. Nano Lett. 19, 5077–5085 (2019).

Yeh, C. H., Cao, W., Pal, A., Parto, K. & Banerjee, K. Area-selective-CVD technology enabled top-gated and scalable 2D-heterojunction transistors with dynamically tunable Schottky barrier (IEEE, 2019).

Kamaei, S. et al. An experimental study on mixed-dimensional 1D–2D van der Waals single-walled carbon nanotube-WSe2 hetero-junction. IEEE Electron Device Lett. 41, 645–648 (2020).

Jadwiszczak, J. et al. Mixed-dimensional 1D/2D van der Waals heterojunction diodes and transistors in the atomic limit. ACS Nano 16, 1639–1648 (2022).

Li, X. et al. One-dimensional semimetal contacts to two-dimensional semiconductors. Nat. Commun. 14, 111 (2023). This study shows sub-1 nm ultra-short contact lengths for 2DM transistors.

Chuang, S. et al. MoS2 P-type transistors and diodes enabled by high work function MoOx contacts. Nano Lett. 14, 1337–1342 (2014).

Wang, Y. et al. P-type electrical contacts for 2D transition-metal dichalcogenides. Nature 610, 61–66 (2022). This study shows high-performance nearly ohmic P-type contact for 2DM transistors.

Carter, R. J. et al. Passivation and interface state density of SiO2/HfO2-based/polycrystalline-Si gate stacks. Appl. Phys. Lett. 83, 533–535 (2003).

Stesmans, A. Interaction of Pb defects at the (111)Si/SiO2 interface with molecular hydrogen: simultaneous action of passivation and dissociation. J. Appl. Phys. 88, 489–497 (2000).

Knobloch, T. et al. Improving stability in two-dimensional transistors with amorphous gate oxides by Fermi-level tuning. Nat. Electron. 5, 356–366 (2022).

Illarionov, Y. Y. et al. Insulators for 2D nanoelectronics: the gap to bridge. Nat. Commun. 11, 3385 (2020).

Knobloch, T. et al. The performance limits of hexagonal boron nitride as an insulator for scaled CMOS devices based on two-dimensional materials. Nat. Electron. 4, 98–108 (2021).

Lenzlinger, M. & Snow, E. H. Fowler–Nordheim tunneling into thermally grown SiO2. J. Appl. Phys. 40, 278–283 (2003).

Chason, E. et al. Ion beams in silicon processing and characterization. J. Appl. Phys. 81, 6513–6561 (1997).

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Vu, Q. A. et al. Near-zero hysteresis and near-ideal subthreshold swing in h-BN encapsulated single-layer MoS2 field-effect transistors. 2D Mater. 5, 031001 (2018). This paper shows high-quality vdW-stacked dielectrics for 2DM transistors.

Cassabois, G., Valvin, P. & Gil, B. Hexagonal boron nitride is an indirect bandgap semiconductor. Nat. Photon. 10, 262–266 (2016).

Illarionov, Y. Y. et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. Nat. Electron. 2, 230–235 (2019).

Huang, J.-K. et al. High-κ perovskite membranes as insulators for two-dimensional transistors. Nature 605, 262–267 (2022). This paper shows ultra-thin equivalent oxide thickness dielectric integration on a 2DM transistors.

Lu, Z. et al. Wafer-scale high-κ dielectrics for two-dimensional circuits via van der Waals integration. Nat. Commun. 14, 2340 (2023). This paper provides a large-scale high-k dielectric transfer process for 2DM transistors.

Hisamoto, D. et al. FinFET — a self-aligned double-gate MOSFET scalable to 20 nm. IEEE Trans. Electron Devices 47, 2320–2325 (2000).

Park, J. C. et al. High performance amorphous oxide thin film transistors with self-aligned top-gate structure (IEEE, 2009).

Wann, C. et al. Channel profile optimization and device design for low-power high-performance dynamic-threshold MOSFET (IEEE, 1996).

Balogh, L. Design and application guide for high speed MOSFET gate drive circuits (Texas Instruments, 2001).

English, C. D., Smithe, K. K. H., Xu, R. L. & Pop, E. Approaching ballistic transport in monolayer MoS2 transistors with self-aligned 10 nm top gates. (IEEE, 2016). This study provides early attempts at a self-aligned process for 2DM transistors at 10 nm gate length.

Sangwan, V. K. et al. Self-aligned van der Waals heterojunction diodes and transistors. Nano Lett. 18, 1421–1427 (2018).

Li, X. et al. Large-area synthesis of high-quality and uniform graphene films on copper foils. Science 324, 1312–1314 (2009).

Hao, Y. et al. The role of surface oxygen in the growth of large single-crystal graphene on copper. Science 342, 720–723 (2013).

Xu, X. et al. Ultrafast epitaxial growth of metre-sized single-crystal graphene on industrial Cu foil. Sci. Bull. 62, 1074–1080 (2017).

Zhang, X. et al. Epitaxial growth of 6 in. single-crystalline graphene on a Cu/Ni (111) film at 750 °C via chemical vapor deposition. Small 15, 1805395 (2019).

Li, P. et al. Wafer-scale growth of single-crystal graphene on vicinal Ge(001) substrate. Nano Today 34, 100908 (2020).

Li, J. et al. Wafer-scale single-crystal monolayer graphene grown on sapphire substrate. Nat. Mater. 21, 740–747 (2022).

Lee, Y.-H. et al. Synthesis of large-area MoS2 atomic layers with chemical vapor deposition. Adv. Mater. 24, 2320–2325 (2012).

Zhang, J. et al. Scalable growth of high-quality polycrystalline MoS2 monolayers on SiO2 with tunable grain sizes. ACS Nano 8, 6024–6030 (2014).

Kang, K. et al. High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. Nature 520, 656–660 (2015).

Fu, D. et al. Molecular beam epitaxy of highly crystalline monolayer molybdenum disulfide on hexagonal boron nitride. J. Am. Chem. Soc. 139, 9392–9400 (2017).

Wang, Q. et al. Wafer-scale highly oriented monolayer MoS2 with large domain sizes. Nano Lett. 20, 7193–7199 (2020).

Yang, P. et al. Epitaxial growth of centimeter-scale single-crystal MoS2 monolayer on Au(111). ACS Nano 14, 5036–5045 (2020).

Feng, X. et al. Self-selective multi-terminal memtransistor crossbar array for in-memory computing. ACS Nano 15, 1764–1774 (2021).

Gao, Y. et al. Large-area synthesis of high-quality and uniform monolayer WS2 on reusable Au foils. Nat. Commun. 6, 8569 (2015).

Chen, J. et al. Chemical vapor deposition of large-size monolayer MoSe2 crystals on molten glass. J. Am. Chem. Soc. 139, 1073–1076 (2017).

Xu, X. et al. Seeded 2D epitaxy of large-area single-crystal films of the van der Waals semiconductor 2H MoTe2. Science 372, 195–200 (2021). This study shows large-area growth of P-type 2DMs.

Wang, Q. et al. Layer-by-layer epitaxy of multi-layer MoS2 wafers. Natl Sci. Rev. 9, nwac077 (2022).

Xia, Y. et al. 12-inch growth of uniform MoS2 monolayer for integrated circuit manufacture. Nat. Mater. 22, 1324–1331 (2023). This study shows large-area, high-quality MoS2 CVD growth in 300 mm wafer.

Wan, Y. et al. Low-defect-density WS2 by hydroxide vapor phase deposition. Nat. Commun. 13, 4149 (2022).

Maxey, K. et al. 300 mm MOCVD 2D CMOS materials for more (than) Moore scaling (IEEE, 2022).

Chen, T.-A. et al. Wafer-scale single-crystal hexagonal boron nitride monolayers on Cu(111). Nature 579, 219–223 (2020).

Lee, Y. et al. Wafer-scale synthesis and transfer of graphene films. Nano Lett. 10, 490–493 (2010).

Wang, J. et al. Dual-coupling-guided epitaxial growth of wafer-scale single-crystal WS2 monolayer on vicinal a-plane sapphire. Nat. Nanotechnol. 17, 33–38 (2022).

Lee, J. S. et al. Wafer-scale single-crystal hexagonal boron nitride film via self-collimated grain formation. Science 362, 817–821 (2018).

Tan, C. et al. Wafer-scale growth of single-crystal 2D semiconductor on perovskite oxides for high-performance transistors. Nano Lett. 19, 2148–2153 (2019).

Leskelä, M. & Ritala, M. Atomic layer deposition (ALD): from precursors to thin film structures. Thin Solid Films 409, 138–146 (2002).

Huang, Y. et al. Universal mechanical exfoliation of large-area 2D crystals. Nat. Commun. 11, 2453 (2020).

Yang, P. et al. Batch production of 6-inch uniform monolayer molybdenum disulfide catalyzed by sodium in glass. Nat. Commun. 9, 979 (2018).

Quellmalz, A. et al. Large-area integration of two-dimensional materials and their heterostructures by wafer bonding. Nat. Commun. 12, 917 (2021). This study shows 2DMs transfer for 300 mm wafer.

Iqbal, M. W. et al. High-mobility and air-stable single-layer WS2 field-effect transistors sandwiched between chemical vapor deposition-grown hexagonal BN films. Sci. Rep. 5, 10699 (2015).

Chen, J. et al. Chemical vapor deposition of large-sized hexagonal WSe2 crystals on dielectric substrates. Adv. Mater. 27, 6722–6727 (2015).

Shi, X. et al. High-performance bilayer WSe2 pFET with record Ids = 425 μA/μm and Gm = 100 at μS/μm Vds = −1 V by direct growth and fabrication on SiO2 substrate (IEEE, 2022).

Irisawa, T., Numata, T., Tezuka, T., Sugiyama, N. & Takagi, S. I. Electron transport properties of ultrathin-body and tri-gate SOI nMOSFETs with biaxial and uniaxial strain (IEEE, 2006).

Uchida, K. et al. Experimental study on carrier transport mechanism in ultrathin-body SOI nand p-MOSFETs with SOI thickness less than 5 nm (IEEE, 2002).

Jones, E. C. & Ishida, E. Shallow junction doping technologies for ULSI. Mater. Sci. Eng. R. Rep. 24, 1–80 (1998).

Chou, A. S. et al. Antimony semimetal contact with enhanced thermal stability for high performance 2D electronics (IEEE, 2021).

Wang, Y. et al. van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. Nature 568, 70–74 (2019).

Kumar, A. et al. Sub-200 Ω·µm alloyed contacts to synthetic monolayer MoS2 (IEEE, 2021).

Smithe, K. K. H., English, C. D., Suryavanshi, S. V. & Pop, E. High-field transport and velocity saturation in synthetic monolayer MoS2. Nano Lett. 18, 4516–4522 (2018).

Liu, W. et al. Role of metal contacts in designing high-performance monolayer n-type WSe2 field effect transistors. Nano Lett. 13, 1983–1990 (2013).

Semiconductor Research Corporation. International Technology Roadmap for Semiconductors: 2011 edition (SRC, 2011).

Wang, J. et al. Integration of high-k oxide on MoS2 by using ozone pretreatment for high-performance MoS2 top-gated transistor with thickness-dependent carrier scattering investigation. Small 11, 5932–5938 (2015).

Goley, P. S. & Hudait, M. K. Germanium based field-effect transistors: challenges and opportunities. Materials 7, 2301–2339 (2014).

McPherson, J. W., Jinyoung, K., Shanware, A., Mogul, H. & Rodriguez, J. Trends in the ultimate breakdown strength of high dielectric-constant materials. IEEE Trans. Electron Devices 50, 1771–1778 (2003).

Acknowledgements

This work was supported by the National Key Research and Development Program (Grant No. 2021YFA1200500), the Innovation Program of Shanghai Municipal Education Commission (Grant No. 2021-01-07-00-07-E00077), the National Natural Science Foundation of China (61925402, 62090032, 62322405, 62374042 and 62004040), Science and Technology Commission of Shanghai Municipality (19JC1416600), Shanghai Pilot Program for Basic Research — FuDan University 21TQ1400100 (21TQ011), Shanghai Rising-Star Program (22QA1400700) and the Young Scientist Project of the MOE innovation platform.

Author information

Authors and Affiliations

Contributions

P.Z. and C.L. provided innovative ideas for the article, and S.Z. and C.L. worked together on the organization and writing of the article. The authors reviewed the novel solutions for channel, contact and dielectric engineering using 2DM to address the scaling challenges at the advanced tech node. Channel engineering for 2DM transistors is reviewed. The authors suppose that further research should be conducted on the PMOS channel. The contact engineering of 2DM transistors is reviewed, and the contact technology of 2DM is summarized in terms of contact resistance, contact length and process temperature compatibility. The authors summarized the three promising dielectrics engineering of 2DM transistors and analysed the advantages and disadvantages of each path. The fabrication processes of 2DM and silicon transistors are compared in this Review, and the importance of self-aligned manufacturing process of 2DM transistors is emphasized. The authors summarized the challenges in translating the performance of individual 2DMs devices into large-scale integration, including large-scale 2DM transfer, as well as controllable high-quality synthesis of 2DM.

Corresponding authors

Ethics declarations

Competing interest

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Zeng, S., Liu, C. & Zhou, P. Transistor engineering based on 2D materials in the post-silicon era. Nat Rev Electr Eng 1, 335–348 (2024). https://doi.org/10.1038/s44287-024-00045-6

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s44287-024-00045-6