Abstract

Crystalline silicon solar cells with regular rigidity characteristics dominate the photovoltaic market, while lightweight and flexible thin crystalline silicon solar cells with significant market potential have not yet been widely developed. This is mainly caused by the brittleness of silicon wafers and the lack of a solution that can well address the high breakage rate during thin solar cells fabrication. Here, we present a thin silicon with reinforced ring (TSRR) structure, which is successfully used to prepare free-standing 4.7-μm 4-inch silicon wafers. Experiments and simulations of mechanical properties for both TSRR and conventional thin silicon structures confirm the supporting role of reinforced ring, which can share stress throughout the solar cell preparation and thus suppressing breakage rate. Furthermore, with the help of TSRR structure, an efficiency of 20.33% (certified 20.05%) is achieved on 28-μm silicon solar cell with a breakage rate of ~0%. Combining the simulations of optoelectrical properties for TSRR solar cell, the results indicate high efficiency can be realized by TSRR structure with a suitable width of the ring. Finally, we prepare 50 ~ 60-μm textured 182 × 182 mm2 TSRR wafers and perform key manufacturing processes, confirming the industrial compatibility of the TSRR method.

Similar content being viewed by others

Introduction

Photovoltaics plays a leading role in achieving the goal of a low-carbon-emission society. Nowadays, crystalline silicon (c-Si) solar cell dominates the photovoltaic (PV) market, with a market share of over 95% owing to their high module efficiencies, long lifespan of more than 25 years as well as high abundance of silicon1. Among them, there is a huge market potential for lightweight and flexible thin c-Si solar cells since they can be integrated with buildings, remote power applications such as electric vehicles and aircrafts2 and wearable electronic devices3. However, they are not yet widely used due to the mechanically brittle nature of c-Si4 and the dramatically increasing trend in breakage rate during cell processing as the thickness of the wafer decreases5,6.

For the above reason, there is a trade-off between thickness and area for thin silicon solar cells. It is very challenging to prepare thin c-Si solar cells with large areas to a very thin thickness. Table 1 summarizes the characteristics of c-Si solar cells with a thickness of ≤ 40 μm reported since 2010. We can see that the vast proportion of the solar cells has an active area of less than 4 cm2, and some of them even have an area of less than 0.03 cm2. At present, the most straight-forward and low-cost route for preparing thin silicon (solar cells) is to process them in a free-standing way, as is done for standard wafers. However, in 2016, CEA-INES reported a drastic increase in the breakage rate from about 10% at 100 μm thickness to a terrible ~96% at 70 μm thickness in their silicon heterojunction (SHJ) pilot line (using 156 × 156 mm2 pseudo-square wafers)6. Even though process and handling adjustments were implemented, a breakage rate of up to 4.5% during the fabrication of 100 μm thick high-temperature diffused junction cells in the pilot production line of Hanwha Q CELLS was reported7. Such high breakage rates lead to unacceptable yield losses and high total production costs. A solution to this fragility is to prepare thin silicon based on a parent substrate, such as epitaxy, spalling, ‘epifree’, silicon-on-insulator (SOI, ‘smart-cut’ process) and micro-machining (Table 1), and some of them require further bonding or transferring of the thin silicon to external supporters to cope with the following solar cell preparation process. Nevertheless, these fabrication processes are too complicated, leading to questions about the viability of these processes for fabricating thin silicon solar cells in a cost-effective way at an industrial scale. Moreover, the thin silicon with hard substrate is not flexible, which limits its range of applications. The challenges of free-standing and supported processing of thin silicon remain to be answered8.

The vast majority of reports are concerned with solving the problem of reduced light absorption in thin silicon solar cells9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,24, while very few works are devoted to addressing the problem of high breakage rate during thin solar cell fabrication. For example, a locally thinned waffle-like cell was proposed for space silicon solar cell in 2000. Strobl et al. reported a 15.8% efficiency silicon solar cell with a thickness of 50 μm in the locally thinned regions and 130 μm for the frames25. But other details of this structure are particularly underreported. There is also a “3-D” wafer technology developed by 1366 technology, Inc. around 2016. It is a multi-crystalline silicon wafer growing technology which forms a wafer directly from molten silicon in a bath-like furnace, with the ability to locally control wafer thickness. Thus, it can produce thin wafers with thick edge26,27. However, it suffers from serious problems: low bulk lifetime, high total thickness variation (TTV) and difficulty in growing very thin framed wafers27. Recently, a technique of blunting pyramidal structure in the marginal regions was proposed by Liu et al. for thin silicon solar cells with a thickness of around 60 μm2. However, for thinner silicon wafers, there could be a lot of breakage before blunting pyramids.

In this contribution, we present a thin silicon with reinforced ring (TSRR) structure at the edge region, which can be used to prepare ultrathin silicon wafers with a large area and provide support throughout the solar cell preparation process to reduce the breakage rate. Then with the help of COMSOL Multiphysics, we investigated the mechanical properties of TSRR structure and the conventional all-thin silicon (ATS) structure, and the simulation results showed that the reinforced ring of TSRR structure can distribute a large amount of stress when subjected to external forces, thus making the central thin silicon region of TSRR structure bear a smaller force compared to ATS structure. We further prepared solar cells with TSRR structure, where all process steps are done in a free-standing way, and achieved an efficiency of 20.33% (certified 20.05%) on 28-μm silicon solar cell with all dopant-free and interdigitated back contacts. Meanwhile, the breakage rate of each process step of solar cell fabrication with both structures was tracked. To gain an in-depth understanding of the effect of TSRR structure on the optoelectrical performance of solar cells, based on TCAD numerical simulations, we investigated the carrier transport mechanism of the solar cell with TSRR structure, and the impact of the thickness of the central thin silicon region and the width of the reinforced ring on the solar cell performance. Finally, we prepared 50 ~ 60-μm textured 182 × 182 mm2 TSRR wafers and performed screen printing, high-temperature and wet manufacturing processes, which confirms the industrial compatibility of the TSRR method.

Results

Preparation of TSRR structure

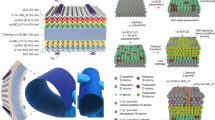

Figure 1a shows preparation process for the TSRR structure. Generally, thick silicon wafers are etched into ATS wafers with desired thickness by alkaline solutions such as Potassium hydroxide (KOH) and Tetramethylammonium hydroxide (TMAH). However, the ATS structure is easily broken down during thin silicon solar cell fabrication, and it is important to note that it is not possible to prepare thinned 4-inch wafers with a thickness of <10 μm with ATS structure based on our experiments. We proposed a method to fabricate the TSRR structure, which requires only 3 more steps with common devices in photovoltaic factories for mass production: first depositing 70 nm silicon nitride (SiNx) on both sides of the normal thick silicon wafers by plasma enhanced chemical vapor deposition (PECVD) or low pressure chemical vapor deposition (LPCVD), then removing the SiNx from the central region of one side using a die, laser or photolithographic to make opening, and finally etching the wafer in alkaline solution to the desired thickness. Thanks to the protection of SiNx layer, the silicon in the edge region of the wafer maintains its original thickness, thus forming a reinforced ring. Figure1b (top) displays a thinned 4-inch wafer with TSRR structure being measured by a handheld thickness gauge (reading 10 μm), its real thickness is 4.7 μm, as depicted in Fig. 1b (bottom), which is the scanning electron microscope (SEM) image of the cross section. The width and thickness of the reinforced ring are 2 ~ 4 mm and 192 μm, respectively. To the best of our knowledge, this is the largest area of free-standing monocrystalline silicon with a thickness of <5 μm reported so far. Figure1c (top) displays the corresponding measurement (reading 31 μm) by handheld thickness gauge of the thinned 4-inch wafer with ATS structure, and its exact thickness is 23.3 μm as shown in Fig. 1c (bottom). We can find that the thinned 23.3-μm wafer with ATS structure is bending downward under gravity only. However, this flexibility is not desired in the processing or testing stages, as it tends to cause breakage. In contrast, the 4.7-μm thin silicon wafer with reinforced ring still remains horizontal under gravity, demonstrating the supporting role of the reinforced ring. We also offer the SEM image about the boundary of the reinforced ring and the central thin silicon region in Supplementary Fig. 1.

a Preparation process for TSRR structure. Thinned 4-inch wafers with b TSRR structure and c all-thin silicon (ATS) structure are measured by handheld thickness gauge (top) and the corresponding SEM images of the cross section (bottom). It should be noted that thinned 4-inch wafers with a thickness of <10 μm with ATS structure cannot be prepared using alkaline solution etching. d Optical image of the 4.7-μm 4-inch wafer with TSRR structure underneath white light illumination, the letters “SJTU, SYSU” on the paper below the thin silicon wafer are clearly visible. e Flexibility performance of the thinned wafer in d. Note that we can control the flexibility of the wafer with TSRR structure by adjusting the thickness of the reinforced ring. f Fully thin silicon wafer with an area of 60.8 cm2 with the reinforced ring cut off and g its flexibility performance, the bending radius is 1 mm.

Figure 1d is the optical image of the 4.7-μm 4-inch wafer with TSRR structure underneath white light illumination, the letters “SJTU, SYSU” on the paper below the thin silicon wafer are clearly visible, which reflects its ultra-thinness and high red light transmission10. At the same time, based on the color uniformity shown here, we can also see that the thickness of the wafer is fairly uniform, and according to our further quantitative measurements on the thickness uniformity, as demonstrated in Supplementary Fig. 2, the TTV for this thin silicon preparation method is within 6 μm. Despite of the thick reinforced ring, it is still bendable, as exhibited in Fig. 1e. And its flexibility depends on the combined bending performance of the reinforced ring and the central thin silicon region. This means that we can control the flexibility of the entire wafer by adjusting the thickness of the reinforced ring. If high bending performance is required, we can cut off the reinforced ring with a laser in the last process step. Figure 1f shows a fully thin wafer with an area of 60.8 cm2 obtained in this way. And it has a bending radius of 1 mm as revealed in Fig. 1g.

Mechanical properties of ATS and TSRR structures

Stress profile and deformation of ATS and TSRR structure in three cases during fabrication process in which the breakage rates are very high, were investigated by shell module under structural mechanics branch in COMSOL Multiphysics. Noted that since it is not possible to prepare thinned 4-inch wafers with a thickness of <10 μm with ATS structure as mentioned earlier, 30 μm is simulated for the ATS structure here. And the corresponding thickness is 30 μm for the central thin silicon region and 210 μm for the reinforced ring of the TSRR structure. All silicon wafers are 4 inches (10 cm) in size and the width of reinforced ring is 3 mm.

The first case is self-weight (handling or transferring). Figure 2a shows simplified schematic diagram of thin silicon wafer with a fixed position under the effect of gravity (corresponding to Fig. 1b and c). In the simulation, the vertical downward displacement of the point furthest from the fixed position is 14.3 mm for ATS structure and 2.5 mm for TSRR structure, as depicted in Supplementary Fig. 3. This is consistent with the experiments in which the displacement is ~16 mm for 24-μm wafer with ATS structure and ~3 mm for 6-μm wafer with TSRR structure. This confirms the validity of our simulation results. The Von Mises stress profile of the ATS structure (top) and the TSRR structure (bottom) in this case are demonstrated in Fig. 2b. The maximum stress is 7.21 × 107 N/m2 = 72.1 MPa for ATS structure and the maximum stress point is located at the left end of the fixed position, i.e., near the overhanging area. In contrast, the maximum stress of TSRR structure is 51.8 MPa, which is smaller than 72.1 MPa for ATS structure, and the maximum stress point is located at the right end of the fixed position, i.e., near the reinforced ring. In addition, the further away from the fixed position the less stress is suffered for ATS structure, while this is not the case for TSRR structure. We can observe that the boundary between the reinforced ring and the central thin silicon region undergo a large amount of stress, which helps the central thin region to bear less stress than the ATS structure. A clearer comparison can be found in Fig. 2c, it is the stress distribution along the cut line σ1 in Fig. 2b. The gray dashed line indicates the boundary between the reinforced ring and the central thin silicon region. It is clear that the stress in the central thin silicon region except near the boundary of TSRR structure are smaller than that of ATS structure. This fully illustrates the stress-sharing role of the reinforced ring.

a Simplified schematic diagram of thin silicon wafer with a fixed position under the effect of gravity (corresponding to Fig. 1b, c), b Corresponding Von Mises stress profile of the ATS (top) and the TSRR (bottom) structures, and c the Von Mises stress distribution along the cut line σ1 in (b). d Simplified schematic diagram of thin silicon wafers during wet processing, where, ①: Floatation due to buoyant force and bubbles. ②: Stiction due to surface tension. The corresponding e Von Mises stress profile of the ATS (top) and the TSRR (bottom) structures, and f Von Mises stress distribution along the cut line σ2 in (e), where, the central circular area with a radius of 5 mm is subjected to a total force of 0.2 N along the direction perpendicular to the surface of the wafer with the outermost edge of the wafers fixed. g Simplified schematic diagram of thin silicon wafer during screen printing, the corresponding h Von Mises stress profile of the ATS (top) and the TSRR (bottom) structures, and i Von Mises stress distribution along the cut line σ3 in (h), where, crossed line loads of 3 N/m are applied with the outermost edge of the wafers fixed. The gray dashed lines in (c), (f) and (i) indicate the boundary between the reinforced ring and the central thin silicon region. Source data are provided as a Source Data file.

Note that the state in Fig. 2a is similar to that when handling or transferring thin silicon wafers in experiments as the only external force during these processes is gravity. Handling and transferring have been experimentally demonstrated to be particularly prone to cause breakage for ATS structure7,8, which means the breakage rate can be reduced during handling and transferring by using TSRR structure based on the results of Fig. 2b. In fact, as displayed in Supplementary Fig. 4, tweezers can be gripped at the reinforced ring instead of the central thin silicon region when we are handling or transferring the TSRR structure, which can further reduce the breakage rate.

The second case is wet process. In the preparation process of silicon solar cells, wet process is a necessary, such as anisotropic etching of silicon to form random pyramids, standard Radio Corporation of America (RCA) cleaning and simplest cleaning with deionized water. Figure 2d displays the states of thin silicon wafers during wet processing. Because the thin wafers are so light in mass, they float up due to buoyant force and bubbles (①). It was found through our experiments that a severe case is stiction due to surface tension, as this often leads to wafer breakage for ultrathin wafers when the edges of the wafers are constrained by the Teflon basket (②) or when trying to separate them. Assuming that the central circular area with a radius of 5 mm is subjected to a total force of 0.2 N along the direction perpendicular to the surface of the wafer during wet process. The Von Mises stress profile of the ATS (top) and the TSRR structure (bottom) in this case are demonstrated in Fig. 2e (note the outermost edge of the wafers is fixed). The maximum and minimum stresses are 316.0 MPa and 62.4 MPa respectively for ATS structure and the maximum stress point is located at the center of the wafer. With regard to TSRR structure, the maximum stress is only 10.2 MPa, which is down to 3% of the maximum stress of ATS structure, and this is even 83.7% smaller than the minimum stress of ATS structure. The maximum stress point is slightly deviated from the center of the wafer and closer to the reinforced ring. The minimum stress is 0.4 MPa, which is 2 orders of magnitude smaller than the minimum stress of ATS structure. Figure 2f provides a comparison of the stress distribution along the cut line σ2 in Fig. 2e for the two structures. Obviously, the suffered stress of TSRR structure is always less than that of ATS structure. Similar to Fig. 2c, the stress increases sharply at the boundary of TSRR structure. In fact, based on our bending experiments of thin silicon with different thicknesses and corresponding simulation results offered in Supplementary Fig. 5, we obtain that the wafer breaks when the maximum Von Mises stress is greater than 345 ~ 533 MPa, which is compatible with the reported fracture strength of crystalline silicon with a value of 80 ~ 520 MPa (varying with the surface damage of silicon wafer)28,29,30,31. This means that the ATS structure with this state of stress shown in Fig. 2e (top) is likely broken, while the TSRR structure stays safe.

It is due to the stress-sharing effect of the reinforced ring that we can prepare 4.7-μm 4-inch wafers with TSRR structure, while it is not possible to prepare thinned 4-inch wafers with a thickness of <10 μm with ATS structure by alkaline solution etching wet process. We can clearly see the behaviors of both structures under complex stresses during the alkaline solution etching wet process in the Supplementary Movie 1.

The third case is screen printing. In the industrial production of large-area silicon solar cells, electrodes are prepared by screen printing, which is probably the mechanical process with the highest probability of causing silicon breakage during the free-standing processing of thin silicon solar cells, since a large load from squeegee and adhesion force from metal paste will be applied to them8. Suppose that crossed line loads of 3 N/m are applied to the thin silicon wafer as shown in Fig. 2g, which is a simplified stress state of the thin silicon wafer under screen printing. The resulted Von Mises stress profile of the ATS structure (top) and the TSRR structure (bottom) are demonstrated in Fig. 2h (note the outermost edge of the wafers is fixed). The maximum and minimum stresses are 271.0 MPa and 69.2 MPa respectively for ATS structure and the maximum stress point is still in the center of the wafer. Notice that the stress is high near the outermost edge because it is fixed in the simulation. Concerning the TSRR structure, the maximum stress is an order of magnitude smaller than that of ATS structure, which is 23.4 MPa. And the minimum stress is only 0.00768 MPa. The maximum stress point located at the boundary between the reinforced ring and the central thin silicon region. A better comparison of the stress distribution along the cut line σ3 in Fig. 2h is presented in Fig. 2i. Same to Fig. 2f, the tolerated stress of TSRR structure is always less than that of ATS structure and there is a steep increase in stress at the boundary of TSRR structure.

In addition, it is important to emphasize that, studies have shown that the cracking starts at the edge of the wafer and breakage occurs due to crack propagation2,8,32, and Wieghold et al.32, discovered that the critical force required to break a wafer decreases as thickness decreases based on their simulations of edge micro-crack propagation in wafers with different thicknesses, which implies the quality of the edges of the wafer is critical especially for thin wafer. Fortunately, our proposed thick reinforced ring of TSRR structure enables edges reinforcement of thin silicon wafer, which means that the reinforced ring not only shares the stress but also raise the critical force of breakage for thin silicon wafer.

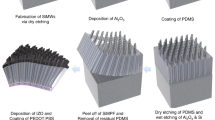

Fabrication of solar cells with TSRR structure

Using TSRR structure, we fabricated free-standing thin silicon solar cells with all dopant-free and interdigitated back contacts to confirm that this structure is suitable for solar cells. It is worth stating that the TSRR structure is applicable to any silicon technology such as passivated emitter and rear cell (PERC)33, silicon heterojunction (SHJ)34,35, tunnel oxide passivating contact (TOPCon)36,37 as well as dopant-free passivating contact38,39, and both front and back contacts (FBC) and interdigitated back contacts (IBC) structures34,40. While there are limitations to use those technologies on thin silicon wafers with substrate. Since one side of the thin wafer needs to be in contact with the substrate for support, the substrate becomes a barrier when processing this side, leading to complex preparation processes, such as removing the substrate on this side and attaching another carrier on the opposite side12,16. The flow chart in our experiments is given in Fig. 3a, the process began with the free-standing samples with TSRR structure etched from 150-μm thick silicon, n-type, single-crystalline wafers by the method shown in Fig. 1a. The thin samples were then textured and passivated. All dopant-free and back contacts were evaporated by a thermal evaporator at ambient temperature. Details of the process can be found in Methods section.

a Flow chart for free-standing thin silicon solar cells with all dopant-free and interdigitated back contacts using TSRR structure. b SEM image of the cross section of the champion thin silicon solar cell in our experiments. c Light J-V curves of the champion 28-μm thin cell and the 150-μm control sample. d The corresponding reflection (R), external quantum efficiency (EQE), and internal quantum efficiency (IQE) of the champion thin sample. The inset shows our real TSRR solar cell sample. Source data are provided as a Source Data file.

Figure 3b gives a SEM image of the cross section of the champion thin silicon solar cell in our experiments, its thickness is 28 μm and the height of the random pyramids is ~ 2 μm. The light current density-voltage ( J-V) curves of the champion thin cell and the 150-μm control sample are presented in Fig. 3c. A JSC of 36.64 mA ‧ cm−2, a VOC of 749.1 mV, an FF of 74.08% and an efficiency of 20.33% was achieved on 28-μm silicon solar cell. It is the highest efficiency reported for thin silicon solar cells with a thickness of <35 μm according to Table 1. The efficiency of the 150-μm control sample was 21.65% with a JSC of 40.37 mA ‧ cm−2, a VOC of 727.0 mV and an FF of 73.77%. The active areas of both of them are 1.007 cm2 due to device limitations in our lab. Despite being more than four times thinner, the champion thin cell achieves 93.9% of the efficiency of the original 150-μm thick silicon control sample. The main gain is a 22.1 mV boost in VOC, which is attributed to a reduction in bulk recombination41. The 28-μm thin device achieved a certified efficiency of 20.05% at a credible third-party photovoltaic laboratory (Supplementary Fig. 6). The corresponding reflection (R), external quantum efficiency (EQE), and internal quantum efficiency (IQE) obtained for the champion thin sample are shown in Fig. 3d, and the inset shows the photo of our real solar cell with TSRR structure. The integrated current density JEQE extracted from the EQE is 36.63 mA ‧ cm−2 and the total reflection is 6.38%. More details and improvement of this type of dopant-free IBC solar cell can be found in our previous works39,42.

Meanwhile, numbers of sample breakage of the two structures during thinning, texturing, vacuuming, taping, handling and transferring processes were tracked, as shown in Table 2. As for the ATS structure, there were 20 samples in total for 21 ~ 29- μm group and 10 samples in total for 51 ~ 57-μm group. The area for all the samples was 2.4 × 2.8 cm2. With respect to TSRR structure, for both 19 ~ 23-μm and 42 ~ 50-μm groups, the number of samples was 10. The whole area of these samples was also 2.4 × 2.8 cm2 and the width of reinforced ring was 3 ~ 5.5 mm. The original thickness of the 50 samples mentioned above was 250 μm. Parentheses in the table represent the number of samples left at the beginning of this stage.

We start by looking at the first group of ATS structure, during the thinning process, i.e., thinning silicon from 250 μm to 21 ~ 29 μm with alkaline solution, 7 samples broke. Followed by 9 samples broke during texturing and 1 sample was fragmented during handling and transferring between the two processes. Surprisingly, the breakage rate was as high as 85% after just these two wet process treatments. We can conclude that the wet processing step is crucial for ultra-thin (<30 μm) silicon wafers, and we need to be careful in order to minimize the breakage rate. In some solar cell preparation processes, vacuuming and taping are required. The numbers of breakage for both processes were 1, but note that at the beginning of taping, there was only one sample left, as there was 1 sample breakage in handling and transferring between them. Therefore, it can be concluded that the breakage rate is >85% for fabricating 21 ~ 29 μm solar cells with an area of 2.4 × 2.8 cm2 using ATS structure. Breakage rate can even increase to 100% if vacuuming and taping are required in the fabrication. As the thickness increases to 51 ~ 57 μm, the breakage rate decreases to 40% for ATS structure. In sharp contrast, the breakage rates of both 19 ~ 23-μm and 42 ~ 50-μm groups were 0% for TSRR structure. The aforementioned results prove that the reinforced ring of TSRR structure can greatly reduce the breakage rate during the preparation of thin silicon solar cells.

Optoelectrical performance of solar cells with TSRR structure

To gain an in-depth understanding of the effect of TSRR structure on the optoelectrical performance of solar cells, we performed a TCAD numerical simulation43. And, in order to provide the readers with a better understanding, we simulated the FBC solar cells with TSRR structure instead of the IBC solar cells since the carrier transport mechanism of the FBC solar cells is simpler. We first investigated the direction of carrier transport of the solar cell with TSRR structure. We call the width W1 of the reinforced ring as a percentage of the width W2 of the whole solar cell Ratio (W1/ W2). For the purpose of providing a clearer picture of the direction of current density, we provide the simulated light current density map under AM1.5 G solar spectrum with Ratio = 10% in Fig. 4a, the inset shows the SHJ structure in the simulation (not scaled). The thicknesses of the central thin silicon region and the reinforced ring are 30 μm and 250 μm, respectively. Other parameters used in this simulation are given in Methods section. The direction of current transport represented by the gray arrows in the central thin silicon region is the same as that of conventional FBC solar cells. While the direction of current transport represented by the orange arrows is unique due to the presence of reinforced ring, since the photogenerated carriers generated at the reinforced ring region need to transport to the metal electrodes to be collected. This movement of carriers affects the FF of solar cells.

a Simulated light current density map under AM1.5 G solar spectrum when applied voltage is 0 with Ratio = 10%. Ratio is the width of the reinforced ring (W1) as a percentage of the width of the whole solar cell (W2). The inset shows the SHJ structure in the simulation (not scaled). The direction of current transport represented by the gray arrows in the central thin silicon region is the same as that of conventional FBC solar cells. While the direction of current transport represented by the orange arrows is unique due to the presence of reinforced ring. Calculated b JSC, c VOC, d FF and e η with varying the thickness of the central thin silicon region and Ratio. Source data are provided as a Source Data file.

The effect of the thickness of the central thin silicon region and Ratio on optoelectrical performance of solar cells are detailed in Fig. 4b–e. We all know that thicker silicon body absorbs more light, resulting in a larger JSC. Therefore, as Ratio increases, i.e., the width of the 250-μm reinforced ring expands, more light can be absorbed and JSC grows, as depicted in Fig. 4b. Similarly, the bulk recombination is reduced as the thickness of silicon decreases, leading to a boost in VOC. Consequently, VOC increases with decreasing the thickness of the central thin silicon region and Ratio as shown in Fig. 4c. As for FF, FF increases as the thickness decreases since the longitudinal distance required for carrier transport to the electrodes decreases for conventional FBC solar cells. With regard to FBC solar cells with TSRR structure, as mentioned above, the photogenerated carriers in the reinforced ring region need to transport to the metal electrodes to be collected, and the number of these carriers is related to the width of the reinforced ring. As a result, when Ratio increases (0 <Ratio <25%), the number of these carriers that need to travel more distance before being collected increases, and thus the FF decreases. But when Ratio is particularly large (Ratio > 30%), the resistance of longitudinal transport of these carriers decreases and FF starts to increase, as exhibited in Fig. 4d. The trend of the resulted efficiency is presented in Fig. 4e. These results suggest to us that the value of Ratio should ideally be less than ~10% to maintain high efficiency. The above principles also apply to IBC solar cells with TSRR structure. Moreover, we provide comparison of the optoelectrical performance of the ATS and TSRR solar cells with both FBC and IBC structures as demonstrated in Supplementary Fig. 7 and Fig. 8 to give the readers a clearer picture of the TSRR solar cells.

Industrial compatibility of TSRR structure

To validate the industrial compatibility of TSRR structure, we further prepared textured TSRR wafers and performed some key manufacturing processes for mass production of silicon solar cells based on 182 × 182 mm2 pseudo-square wafers with an original thickness of 150 μm which are generally used in industry.

First, we prepared textured TSRR wafers starting from 182×182 mm2 pseudo-square wafers with a thickness of 150 μm. For all TSRR wafers below, the thickness and width of the reinforced ring are 150 μm and 15 mm, respectively, i.e., the Ratio is 8.2%. According to our experiments, the total breakage rate is 100% (20/20) for thinning the wafers with ATS structure from 150 μm to 40 μm and then cleaning by deionized water. In contrast, the total breakage rate is 0% (0/10) for preparing 40-μm TSRR wafers and then texturing. Figure 5a displays a 20-μm textured TSRR wafer and the thinnest textured silicon wafer we have successfully fabricated was as low as 14 μm.

a 20-μm textured wafer with TSRR structure. b The front side of a 60-μm textured TSRR wafer after screen printing and c its flexibility performance. d The 60-μm textured TSRR wafer after multiple high-temperature and wet manufacturing processes. Note, all used wafers are based on 182 × 182 mm2 pseudo-square wafers with an original thickness of 150 μm.

Then we successfully performed screen printing at 170 °C using low-temperature silver paste on 60-μm textured TSRR wafers as shown in Fig. 5b. And its flexibility performance is demonstrated in Fig. 5c. The breakage rate during this process is 0% (0/5). We should admit that there are finger interruptions at the boundary of the reinforced ring and the central thin silicon region because of the steep slopes there. This may require further optimization of screen printing or development of new metallization methods such as metal plating44. We think this is acceptable since this is the world’s first attempt at a manufacturing process for this kind of thin structure, and there are still some processing details to be worked out together. What’s more, if we prepare IBC solar cells whose back side is flat as shown in Fig. 3a, or if we decide to use this thin silicon structure with the reinforced ring cut off when it comes to applying it in some scenarios, the finger interruptions will be no longer an issue.

Last, using a total number of 57 pseudo-square wafers with textured TSRR structure with a thickness of 50 ~ 60 μm, we performed some high-temperature and wet manufacturing processes which are essential for mass production of silicon solar cells. Some pictures during these processes were recorded as shown in Supplementary Fig. 9. We also tracked the numbers of sample breakage in main process steps as shown in Table 3, and these steps include (1) previous RCA cleaning, (2) front-side boron diffusion, (3) back-side thermal SiO2 at 1050 °C, (4) single-side SiO2 removal, (5) alkali polishing, (6) p+ doped poly-Si deposition at 430 °C and annealing at 900 °C, (7) front-side phosphosilicate glass (PSG) removal, (8) RCA cleaning, (9) Al2O3 deposition by atomic layer deposition (ALD) for surface passivation, (10) front-side and (11) back-side PECVD SiNx at 520 °C as ARC. The sample after going through all the above steps is shown in Fig. 5d. Note, ① after step (1), one sample broke when transferring; ② after step (6), 13 samples broke by accident, which should not be included in the breakage count. We can find that the breakage rate is 0% in these high-temperature processes, and most of the breakages occur in the wet processes, which is consistent with the results in Table 2. Breakage rate can be reduced by adjusting some operational details in these steps to make them more suitable for processing thin silicon.

According to above results, we can conclude that our TSRR method is industrial compatible.

Discussion

In summary, we present a TSRR structure, which requires only 3 more steps with common devices in photovoltaic factories for mass production, and free-standing 4-inch 4.7-μm crystalline silicon wafer (Ratio ≈ 3%) was successfully prepared by this method. This is the largest area of free-standing monocrystalline silicon with a thickness of <5 μm reported so far based on our knowledge. Then with the help of COMSOL Multiphysics, we investigated the mechanical properties of TSRR structure and ATS structure under three cases, and the simulation results revealed that the reinforced ring of TSRR structure can share a large stress when subjected to external forces, thus making the central thin silicon region of TSRR structure bear a smaller force compared to ATS structure. We further prepared solar cells with TSRR structure and obtained an efficiency of 20.33% (certified 20.05%) on 28-μm silicon solar cell with all dopant-free and interdigitated back contacts, which is the highest efficiency reported for thin silicon solar cells with a thickness of <35 μm. Meanwhile, the breakage rate of each process of solar cell fabrication with both structures were tracked. The results demonstrated that the breakage rate of 21 ~ 29-μm group with an area of 2.4 × 2.8 cm2 was 85% ~100% for ATS structure, while the breakage rate of 19 ~ 23-μm group with a whole area of 2.4 × 2.8 cm2 was 0% for TSRR structure. The above simulations and experiments confirmed that the reinforced ring can provide support throughout the solar cell preparation process and thus greatly suppressing the breakage rate. Then, based on TCAD numerical simulations, we investigated the carrier transport mechanism of the solar cell with TSRR structure, and the impact of thickness of the central thin silicon region and the width of the reinforced ring on the solar cell performance, which suggested that the value of Ratio should ideally be less than ~10% to maintain high efficiency. Finally, we prepared 50 ~ 60-μm textured TSRR wafers (Ratio = 8.2%) based on 182 × 182 mm2 pseudo-square wafers with an original thickness of 150 μm, and then performed screen printing, high-temperature and wet manufacturing processes, which confirms the industrial compatibility of TSRR structure. We believe that this TSRR method is a feasible solution for the mass production of thin silicon solar cells.

Methods

Fabricating thin dopant-free IBC solar cells

The process began with the free-standing samples with TSRR structure etched from 150-μm thick silicon, n-type, single-crystalline wafers by the method shown in Fig. 1a. Then both sides of the samples were textured and covered symmetrically with 6 nm intrinsic amorphous silicon (i-a-Si:H) as passivation layer and 85 nm SiNx as antireflection layer by PECVD. The photoresist was subsequently spin-coated on the backside of the samples. Note that the air holes for vacuuming are designed to be under the reinforced ring rather than the central thin silicon region to reduce the breakage rate, as shown in the illustration on the right in Fig. 3a. Next, MoOx (10 nm)/Ag (300 nm) and LiFx (1 nm)/Al (400 nm) films were deposited in the area exposed by ultraviolet (UV) light by thermal evaporation at ambient temperature with metal shadow masks to serve as hole-transport layer (HTL) and electron-transport layer (ETL), respectively. The widths of the HTL and ETL were 1225 μm and 625 μm, respectively, and the space between them was 150 μm.

TCAD simulation

The simulation parameters can be found in Table 4. Shockley-Read-Hall (SRH) recombination, Auger recombination, Fermi-Dirac carrier statistics and bandgap narrowing model are deployed into the simulation.

Reporting summary

Further information on this research is available in the Nature Portfolio Reporting Summary linked to this article.

Data availability

All data generated or analyzed during this study are included in the published article and its Supplementary Information and Source Data files. Source data are provided with this paper.

References

Ballif, C., Haug, F.-J., Boccard, M., Verlinden, P. J. & Hahn, G. Status and perspectives of crystalline silicon photovoltaics in research and industry. Nat. Rev. Mater. 7, 597–616 (2022).

Liu, W. et al. Flexible solar cells based on foldable silicon wafers with blunted edges. Nature 617, 717–723 (2023).

Hwang, I., Um, H.-D., Kim, B.-S., Wober, M. & Seo, K. Flexible crystalline silicon radial junction photovoltaics with vertically aligned tapered microwires. Energ. Environ. Sci. 11, 641–647 (2018).

Zhang, L. & Zarudi, I. Towards a deeper understanding of plastic deformation in mono-crystalline silicon. Int. J. Mech. Sci. 43, 1985–1996 (2001).

Munzer, K. A., Holdermann, K. T., Schlosser, R. E. & Sterk, S. Thin monocrystalline silicon solar cells. IEEE Trans. Electron Dev. 46, 2055–2061 (1999).

Harrison, S. et al. How to deal with thin wafers in a heterojunction solar cell industrial pilot line: first analysis of the integration of cells down to 70 μm in production mode. 32nd Europe. Photovolt. Sol. Energ. Conf. Exhibi. 358-362 (2016).

Terheiden, B. et al. Manufacturing 100-µm-thick silicon solar cells with efficiencies greater than 20% in a pilot production line. Phys. Status Solidi A 212, 13–24 (2015).

Radhakrishnan, S. H. et al. Freestanding and supported processing of sub-70 μm kerfless epitaxial Si and thinned Cz/FZ Si foils into solar cells: An overview of recent progress and challenges. Sol. Energ. Mat. Sol. C. 203, 110108 (2019).

Xue, M. et al. Free-standing 2.7 μm thick ultrathin crystalline silicon solar cell with efficiency above 12.0%. Nano Energy 70, 104466 (2020).

Wang, S. et al. Large-area free-standing ultrathin single-crystal silicon as processable materials. Nano Lett. 13, 4393–4398 (2013).

Branham, M. S. et al. 15.7% Efficient 10-mum-thick crystalline silicon solar cells using periodic nanostructures. Adv. Mater. 27, 2182–2188 (2015).

Depauw, V. et al. Sunlight-thin nanophotonic monocrystalline silicon solar cells. Nano Futures 1, 021001 (2017).

Jeong, S., McGehee, M. D. & Cui, Y. All-back-contact ultra-thin silicon nanocone solar cells with 13.7% power conversion efficiency. Nat. Commun. 4, 2950 (2013).

Yu, K. J. et al. Light Trapping in Ultrathin Monocrystalline Silicon Solar Cells. Adv. Energy Mater. 3, 1401–1406 (2013).

Gaucher, A. et al. Ultrathin Epitaxial Silicon Solar Cells with Inverted Nanopyramid Arrays for Efficient Light Trapping. Nano Lett. 16, 5358–5364 (2016).

Lu, Y. & Lal, A. High-efficiency ordered silicon nano-conical-frustum array solar cells by self-powered parallel electron lithography. Nano Lett. 10, 4651–4656 (2010).

Garnett, E. & Yang, P. Light trapping in silicon nanowire solar cells. Nano Lett. 10, 1082–1087 (2010).

Hwang, I. et al. Effective Photon Management of Non-Surface-Textured Flexible Thin Crystalline Silicon Solar Cells. Cell Rep. Phys. Sci. 1, 100242 (2020).

Li, Y. et al. Quasi-Omnidirectional Ultrathin Silicon Solar Cells Realized by Industrially Compatible Processes. Adv. Electron Mater. 5, 1800858 (2019).

Yan, W., Tao, Z., Gu, M. & Richards, B. S. Photocurrent enhancement of ultrathin front-textured crystalline silicon solar cells by rear-located periodic silver nanoarrays. Sol. Energ. 150, 156–160 (2017).

Zhang, J. et al. High-Performance Ultrathin Organic-Inorganic Hybrid Silicon Solar Cells via Solution-Processed Interface Modification. ACS Appl. Mater. Interfaces 9, 21723–21729 (2017).

Pudasaini, P. R., Sharma, M., Ruiz-Zepeda, F. & Ayon, A. A. Ultrathin, flexible, hybrid solar cells in sub-ten micrometers single crystal silicon membrane. 40th IEEE Photovolt. Spec. Conf. 953-955 (2014).

He, J. et al. Realization of 13.6% efficiency on 20 μm thick Si/organic hybrid heterojunction solar cells via advanced nanotexturing and surface recombination suppression. ACS Nano 9, 6522–6531 (2015).

Lee, S.-M. et al. Printable nanostructured silicon solar cells for high-performance, large-area flexible photovoltaics. ACS Nano 8, 10507–10516 (2014).

Strobl, G. et al. Thin HI-ETA space silicon solar cells with improved end-of-life performance. 28th IEEE Photovolt. Spec. Conf. 1289-1292 (2000).

Lorenz, A., Hofstetter, J., Malkasian, H., Sanderson & L., Mierlo, V. F. 3 Dimensional Direct Wafer product with locally-controlled thickness. 32nd Europe. Photovolt. Sol. Energ. Conf. Exhibi. 310-312 (2016).

Lorenz, A. 1366 Project Automate: Enabling Automation for <$0.10/W High-Efficiency Kerfless Wafers Manufactured in the US. 1366 Technologies, Bedford, MA, United States (2017).

Möller, H. J., Funke, C., Rinio, M. & Scholz, S. Multicrystalline silicon for solar cells. Thin Solid Films 487, 179–187 (2005).

Funke, C., Kullig, E., Kuna, M. & Möller, H. J. Biaxial Fracture Test of Silicon Wafers. Adv. Eng. Mater. 6, 594–598 (2004).

Rupnowski, P. & Sopori, B. Strength of silicon wafers: fracture mechanics approach. Int J. Fract. 155, 67–74 (2009).

Yasutake, K., Iwata, M., Yoshii, K., Umeno, M. & Kawabe, H. Crack healing and fracture strength of silicon crystals. J. Mater. Sci. 21, 2185–2192 (1986).

Wieghold, S. et al. Detection of sub-500-μm cracks in multicrystalline silicon wafer using edge-illuminated dark-field imaging to enable thin solar cell manufacturing. Sol. Energ. Mat. Sol. C. 196, 70–77 (2019).

Blakers, A. W., Wang, A., Milne, A. M., Zhao, J. & Green, M. A. 22.8% efficient silicon solar cell. Appl. Phys. Lett. 55, 1363–1365 (1989).

Lin, H. et al. Silicon heterojunction solar cells with up to 26.81% efficiency achieved by electrically optimized nanocrystalline-silicon hole contact layers. Nat. Energy 8, 789–799 (2023).

Wakisaka, K. et al. More than 16% solar cells with a new ‘HIT’(doped a-Si/nondoped a-Si/crystalline Si) structure. 22nd IEEE Photovolt. Spec. Conf. 887–892 (1991).

Feldmann, F. et al. Tunnel oxide passivated contacts as an alternative to partial rear contacts. Sol. Energ. Mat. Sol. C. 131, 46–50 (2014).

Richter, A. et al. Design rules for high-efficiency both-sides-contacted silicon solar cells with balanced charge carrier transport and recombination losses. Nat. Energy 6, 429–438 (2021).

Allen, T. G., Bullock, J., Yang, X., Javey, A. & De Wolf, S. Passivating contacts for crystalline silicon solar cells. Nat. Energy 4, 914–928 (2019).

Liu, Z. et al. Dual Functional Dopant-Free Contacts with Titanium Protecting Layer: Boosting Stability while Balancing Electron Transport and Recombination Losses. Adv. Sci. 9, 2202240 (2022).

Martin, A. G. Solar cell efficiency tables (Version 61). Prog. Photovolt. Res. Appl. 31, 3–16 (2023).

Herasimenka, S. Y., Dauksher, W. J. & Bowden, S. G. >750 mV open circuit voltage measured on 50 μm thick silicon heterojunction solar cell. Appl. Phys. Lett. 103, 053511 (2013).

Lin, H. et al. Edge effect in silicon solar cells with dopant-free interdigitated back-contacts. Nano Energy 74, 104893 (2020).

Silvaco, Atlas user manual 2019, https://www.silvaco.com/, accessed: August, 2023.

Lennon, A., Yao, Y. & Wenham, S. Evolution of metal plating for silicon solar cell metallisation. Prog. Photovolt. Res. Appl. 21, 1454–1468 (2012).

Danel, A. et al. Silicon heterojunction solar cells with open-circuit-voltage above 750mV. 35th Europe. Photovolt. Sol. Energ. Conf. Exhibi. 444-447 (2018).

Kuzma-Filipek, I. et al. >16% thin-film epitaxial silicon solar cells on 70-cm2 area with 30-µm active layer, porous silicon back reflector, and Cu-based top-contact metallization. Prog. Photovolt. Res. Appl. 20, 350–355 (2012).

Baek, S.-W. et al. Low-cost and flexible ultra-thin silicon solar cell implemented with energy-down-shift via Cd0.5Zn0.5S/ZnS core/shell quantum dots. J. Mater. Chem. A 3, 481–487 (2015).

Saha, S. et al. Single heterojunction solar cells on exfoliated flexible ∼25 μm thick mono-crystalline silicon substrates. Appl. Phys. Lett. 102, 163904 (2013).

He, J. et al. 15% Efficiency Ultrathin Silicon Solar Cells with Fluorine-Doped Titanium Oxide and Chemically Tailored Poly (3,4-ethylenedioxythiophene): Poly (styrenesulfonate) as Asymmetric Heterocontact. ACS Nano 13, 6356–6362 (2019).

Nasser, H., Borra, M. Z., Çiftpınar, E. H., Eldeeb, B. & Turan, R. 14% efficiency ultrathin silicon solar cells with improved infrared light management enabled by hole-selective transition metal oxide full‐area rear passivating contacts. Prog. Photovolt. Res. Appl. 30, 823–834 (2022).

Wang, L. et al. 16.8% efficient ultra-thin silicon solar cells on steel. 28th Europe. Photovolt. Sol. Energ. Conf. Exhibi. 2641-2644 (2013).

Baca, A. J. et al. Compact monocrystalline silicon solar modules with high voltage outputs and mechanically flexible designs. Energ. Environ. Sci. 3, 208 (2010).

Pourshaban, E. et al. Flexible and Semi-Transparent Silicon Solar Cells as a Power Supply to Smart Contact Lenses. ACS Appl. Electron Mater. 4, 4016–4022 (2022).

Dai, H., Yang, L. & He, S. <50-μm thin crystalline silicon heterojunction solar cells with dopant-free carrier-selective contacts. Nano Energy 64, 103930 (2019).

Cruz-Campa, J. L. et al. Microsystems enabled photovoltaics: 14.9% efficient 14μm thick crystalline silicon solar cell. Sol. Energ. Mat. Sol. C. 95, 551–558 (2011).

Bedell, S. W. et al. Kerf-Less Removal of Si, Ge, and III–V Layers by Controlled Spalling to Enable Low-Cost PV Technologies. IEEE J. Photovolt. 2, 141–147 (2012).

Cariou, R., Labrune, M., Roca, I. & Cabarrocas, P. Thin crystalline silicon solar cells based on epitaxial films grown at 165 °C by RF-PECVD. Sol. Energ. Mat. Sol. C. 95, 2260–2263 (2011).

Xue, M. et al. Contact Selectivity Engineering in a 2 µm Thick Ultrathin c-Si Solar Cell Using Transition-Metal Oxides Achieving an Efficiency of 10.8%. ACS Appl. Mater. Interfaces 9, 41863–41870 (2017).

Young, D. L. et al. Characterization of epitaxial film silicon solar cells grown on seeded display glass. 38th IEEE Photovolt. Spec. Conf. 1841-1844 (2012).

Acknowledgements

This work was supported by the Major State Basic Research Development Program of China (Grant No. 2022YFB4200101, W. S.), the National Natural Science Foundation of China (Grant No. 11974242, 11834011, 62034009, 62104268, W. S., W. S., P. G. and H. L.), Inner Mongolia Science and Technology Project (Grant No. 2022JBGS0036, W. S.), Shenzhen Fundamental Research Program (Grant No. JCYJ20200109142425294, P. G.) and Guangdong Basic and Applied Basic Research Foundation (Grant No. 2019B151502053, P. G.).

Author information

Authors and Affiliations

Contributions

H. L., P. G. and W. S. supervised the work. H. L., T. W. and Z. L. conducted the idea and designed the experiments. T. W. conducted the COMSOL and TCAD simulations. T. W. and Z. L. conducted most of the experiments and prepared the manuscript. H. L. assisted with wafers preparation and devices fabrication. H. L., P. G. and W. S. contributed to the revision of the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks the anonymous reviewer(s) for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Source data

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Wu, T., Liu, Z., Lin, H. et al. Free-standing ultrathin silicon wafers and solar cells through edges reinforcement. Nat Commun 15, 3843 (2024). https://doi.org/10.1038/s41467-024-48290-5

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-024-48290-5

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.