Abstract

The adoption of three-dimensional (3D) integration has revolutionized NAND flash memory technology, and a similar transformative potential exists for logic circuits, by stacking transistors into the third dimension. This pivotal shift towards 3D integration of logic arrives on the heels of substantial improvements in silicon device structures and their subsequent scaling in size and performance. Yet, advanced scaling requires ultrathin semiconducting channels, which are difficult to achieve using silicon. In this context, field-effect transistors based on two-dimensional (2D) semiconductors have drawn notable attention owing to their atomically thin nature and impressive performance milestones. In addition, 2D materials offer a broader spectrum of functionalities — such as optical, chemical and biological sensing — that extends their utility beyond simple ‘more Moore’ dimensional scaling and enables the development of ‘more than Moore’ technologies. Thus, 3D integration of 2D electronics could bring us unanticipated discoveries, leading to sustainable and energy-efficient computing systems. In this Review, we explore the progress, challenges and future opportunities for 3D integration of 2D electronics.

Key points

-

2D electronics must overcome several challenges before they can be adopted in commercial semiconductor chips. Some of the major challenges are discussed in the section ‘Towards very-large-scale integration of 2D electronics’.

-

Research efforts in 2D material synthesis and device integration strategies must happen synergistically, with the goal of 3D integration, because silicon technology is already mature, with the most advanced nodes reaching the limits of planar integration in gate-all-around field-effect transistors.

-

3D integration with 2D electronics not only demands the maturity of 2D electronics in the planar dimension but also poses new difficulties in the vertical direction. These difficulties must be thoroughly understood and addressed before 2D materials can be introduced into commercial electronics.

-

2D materials have the potential to enable multifunctional chips by combining logic with memory and sensing in a 3D-integrated chip. Multifunctional chips containing 2D electronics should be developed with the goal of manufacturing task-specific semiconductor chips and thereby addressing various integration challenges.

This is a preview of subscription content, access via your institution

Access options

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

References

Dennard, R. H. et al. Design of ion-implanted MOSFET’s with very small physical dimensions. IEEE J. Solid-State Circ. 9, 256–268 (1974).

Moore, G. E. Cramming more components onto integrated circuits. Electronics 38, 114–117 (1965).

Burg, D. & Ausubel, J. H. Moore’s Law revisited through Intel chip density. PLoS One 16, e0256245 (2021).

Kelleher, B. Celebrating 75 years of the transistor. A look at the evolution of Moore’s Law innovation. In IEEE Int. Electron Devices Meeting (IEDM) 1.1.1–1.1.5 (IEEE, 2022).

Lau, J. H. State-of-the-art of advanced packaging. In Chiplet Design and Heterogeneous Integration Packaging (ed. Lau, J. H.) 1–99 (Springer Nature, 2023).

Chen, M. F., Chen, F. C., Chiou, W. C. & Yu, D. C. H. System on integrated chips (SoIC(TM) for 3D heterogeneous integration. In 69th Electronic Components and Technology Conf. (ECTC) 594–599 (IEEE, 2019).

Ingerly, D. B. et al. Foveros: 3D integration and the use of face-to-face chip stacking for logic devices. In IEEE Int. Electron Devices Meet. (IEDM) 19.6.1–19.6.4 (IEEE, 2019).

Yu, D. TSMC packaging technologies for chiplets and 3D. In Proc. IEEE Hot Chips 33 (IEEE, 2021).

Lau, J. H. Recent advances and trends in advanced packaging. IEEE Trans. Compon. Packag. Manuf. Technol. 12, 228–252 (2022).

Lu, D. & Wong, C. P. (eds) Materials for Advanced Packaging Vol. 181 (Springer, 2009).

Badaroglu, M. More Moore. In IEEE Int. Roadmap for Devices and Systems Outbriefs 1–38 (IEEE, 2021).

Vinet, M. et al. Monolithic 3D integration: a powerful alternative to classical 2D scaling. In SOI-3D-Subthreshold Microelectronics Technology Unified Conf. (S3S) https://doi.org/10.1109/S3S.2014.7028194 (2014).

Shulaker, M. M. et al. Monolithic 3D integration: a path from concept to reality. In Proc. Design, Automation & Test in Europe Conf. Exhib. (DATE ’15) 1197–1202 (2015).

Dhananjay, K., Shukla, P., Pavlidis, V. F., Coskun, A. & Salman, E. Monolithic 3D integrated circuits: recent trends and future prospects. IEEE Trans. Circ. Syst. II 68, 837–843 (2021).

Courtland, R. The rise of the monolithic 3-D chip. IEEE Spect. 51, 18–19 (2014).

Or-Bach, Z. The monolithic 3D advantage: monolithic 3D is far more than just an alternative to 0.7x scaling. In IEEE Int. 3D Systems Integration Conf. (3DIC) https://doi.org/10.1109/3DIC.2013.6702316 (IEEE, 2013).

Kunio, T., Oyama, K., Hayashi, Y. & Morimoto, M. Three dimensional ICs, having four stacked active device layers. In Int. Tech. Digest on Electron Devices Meet. 837–840 (1989).

Gotzlich, J., Kircher, R., Giesen, K. & Poschl, G. Characterization and simulation of SOI-CMOS devices for 3D-integration. In 19th Eur. Solid State Device Research Conf. (ESSDERC ‘89) 873–876 (1989).

Ferry, D., McGill, T. & Ehrenreich, H. Three dimensional integrated circuits. In Preliminary Reports, Memoranda and Technical Notes of the Materials Research Council Summer Conf. 16 (University of Michigan, Department of Materials and Metallurgical Engineering, 1983).

Bohr M. T. & Young, I. A. CMOS scaling trends and beyond. IEEE Micro. 37, 20–29 (2017).

Ritzenthaler, R. et al. Comparison of electrical performance of co-integrated forksheets and nanosheets transistors for the 2 nm technological node and beyond. In IEEE Int. Electron Devices Meet. (IEDM) 26.2.1–26.2.4 (IEEE, 2021).

Schuddinck, P. et al. Device-, circuit- & block-level evaluation of CFET in a 4 track library. In Symp. VLSI Technology T204–T205 (2019).

Jacob, P. et al. Scaling challenges for advanced CMOS devices. Int. J. High. Speed Electron. Syst. 26, 1740001 (2017).

Uchida, K. et al. Experimental study on carrier transport mechanism in ultrathin-body SOI NAND p-MOSFETs with SOI thickness less than 5 nm. In Digest Int. Electron Devices Meet. 47–50 (IEEE, 2002).

Wei, T. et al. Two dimensional semiconducting materials for ultimately scaled transistors. iScience 25, 105160 (2022).

Das, S. et al. Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 4, 786–799 (2021).

Lemme, M. C., Akinwande, D., Huyghebaert, C. & Stampfer, C. 2D materials for future heterogeneous electronics. Nat. Commun. 13, 1392 (2022).

Zhu, K. et al. The development of integrated circuits based on two-dimensional materials. Nat. Electron. 4, 775–785 (2021).

Kang, K. et al. High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. Nature 520, 656–660 (2015).

Asselberghs, I. et al. Scaled transistors with 2D materials from the 300 mm fab. In IEEE Silicon Nanoelectronics Worksh. (SNW) 67–68 (IEEE, 2020).

O’Brien, K. P. et al. Advancing 2D monolayer CMOS through contact, channel and interface engineering. In IEEE Int. Electron Devices Meet. (IEDM) 11–16 (IEEE, 2021).

Liu, L. et al. Uniform nucleation and epitaxy of bilayer molybdenum disulfide on sapphire. Nature 605, 69–75 (2022). This article describes the uniform nucleation and epitaxy of bilayer MoS2.

Kim, K. S. et al. Non-epitaxial single-crystal 2D material growth by geometric confinement. Nature 614, https://doi.org/10.1038/s41586-022-05524-0 (2023).

Zhu, J. et al. Low-thermal-budget synthesis of monolayer molybdenum disulfide for silicon back-end-of-line integration on a 200 mm platform. Nature Nanotechnol. 18, 456–463 (2023). This article describes low-thermal-budget growth of monolayer MoS2 on a 200 mm platform.

Radisavljevic, A., Radenovic, J., Brivio, V., Giacometti & Kis, A. Single-layer MoS2 transistors. Nature Nanotechnol. 6, 147–150 (2011). This article demonstrates the first MoS2 FET.

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354, 99–102 (2016).

Wachter, S., Polyushkin, D. K., Bethge, O. & Mueller, T. A microprocessor based on a two-dimensional semiconductor. Nat. Commun. 8, 14948 (2017). This article reports a microprocessor based on 2D materials.

Asselberghs, I. et al. Wafer-scale integration of double gated WS2-transistors in 300 mm Si CMOS fab. In IEEE Int. Electron Devices Meet. (IEDM) 40.2.1–40.2.4 (IEEE, 2020).

Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Li, W. et al. Approaching the quantum limit in two-dimensional semiconductor contacts. Nature 613, 274–279 (2023). The article reports very low contact resistance for Sb-contacted transistors.

Jiang, J., Xu, L., Qiu, C. & Peng, L.-M. Ballistic two-dimensional InSe transistors. Nature 616, 470–475 (2023). This article describes 10-nm ballistic InSe field-effect transistors.

Tan, C. et al. 2D fin field-effect transistors integrated with epitaxial high-κ gate oxide. Nature 616, 66–72 (2023). This article reports 2D fin-shaped field-effect transistors.

Chung, Y. Y. et al. First demonstration of GAA monolayer-MoS2 nanosheet nFET with 410μA μm ID 1V VD at 40 nm gate length. In IEEE Int. Electron Devices Meet. (IEDM) 34.5.1–34.5.4 (IEEE, 2022). This article is the first demonstration of a gate-all-around monolayer-MoS2 nanosheet n-field-effect transistor.

Ciarrocchi, F., Tagarelli, A., Avsar & Kis, A. Excitonic devices with van der Waals heterostructures: valleytronics meets twistronics. Nat. Rev. Mater. 7, 449–464 (2022).

Sierra, J. F., Fabian, J., Kawakami, R. K., Roche, S. & Valenzuela, S. O. Van der Waals heterostructures for spintronics and opto-spintronics. Nat. Nanotechnol. 16, 856–868 (2021).

Schaibley, J. R. et al. Valleytronics in 2D materials. Nat. Rev. Mater. 1, (2016).

Miao, F., Liang, S.-J. & Cheng, B. Straintronics with van der Waals materials. npj Quant. Mater. 6, 59 (2021).

Daus et al. High-performance flexible nanoscale transistors based on transition metal dichalcogenides. Nat. Electron. 4, 495–501 (2021).

Akinwande et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Jiang, J., Parto, K., Cao, W. & Banerjee, K. Ultimate monolithic-3D integration with 2D materials: rationale, prospects, and challenges. IEEE J. Electron. Devices Soc. 7, 878–887 (2019).

Lee, Y.-H. et al. Synthesis of large-area MoS2 atomic layers with chemical vapor deposition. Adv. Mater. 24, 2320–2325 (2012).

van der Zande, M. et al. Grains and grain boundaries in highly crystalline monolayer molybdenum disulphide. Nat. Mater. 12, 554–561 (2023).

Schram, T. et al. WS2 transistors on 300 mm wafers with BEOL compatibility. In 2017 47th Eur. Solid-State Device Research Conf. (ESSDERC) 212–215 (2017).

Yang, P. et al. Batch production of 6-inch uniform monolayer molybdenum disulfide catalyzed by sodium in glass. Nat. Commun. 9, 979 (2018).

Dumcenco et al. Large-area epitaxial monolayer MoS2. ACS Nano 9, 4611–4620 (2015).

Yu, H. et al. Wafer-scale growth and transfer of highly-oriented monolayer MoS2 continuous films. ACS Nano 11, 12001–12007 (2017).

Li, T. et al. Epitaxial growth of wafer-scale molybdenum disulfide semiconductor single crystals on sapphire. Nat. Nanotechnol. 16, 1201–1207 (2021).

Fu, J.-H. et al. Oriented lateral growth of two-dimensional materials on c-plane sapphire. Nat. Nanotechnol. 18, 1289–1294 (2023).

Chubarov, M. et al. Wafer-scale epitaxial growth of unidirectional WS2 monolayers on sapphire. ACS Nano 15, 2532–2541 (2021).

Zhu, H. et al. Step engineering for nucleation and domain orientation control in WSe2 epitaxy on c-plane sapphire. Nat. Nanotechnol. 18, 1295–1302 (2023).

Hoang, T. et al. Low-temperature growth of MoS2 on polymer and thin glass substrates for flexible electronics. Nat. Nanotechnol. 18, 1439–1447 (2023).

Chiang, C., Lan, H. Y., Pang, C. S., Appenzeller, J. & Chen, Z. Air-stable P-doping in record high-performance monolayer WSe2 devices. IEEE Electron. Device Lett. 43, 319–322 (2022).

Schranghamer, T. F., Sharma, M., Singh, R. & Das, S. Review and comparison of layer transfer methods for two-dimensional materials for emerging applications. Chem. Soc. Rev. 50, https://doi.org/10.1039/D1CS00706H (2021).

Shim, J. et al. Controlled crack propagation for atomic precision handling of wafer-scale two-dimensional materials. Science 362, 665–670 (2018).

Kang, K. et al. Layer-by-layer assembly of two-dimensional materials into wafer-scale heterostructures. Nature 550, 229–233 (2017).

Phommahaxay, A. et al. The growing application field of laser debonding: from advanced packaging to future nanoelectronics. In Int. Wafer Level Packaging Conf. (IWLPC). https://doi.org/10.23919/IWLPC.2019.8914124 (2019).

Li, M. Y. et al. Wafer-scale Bi-assisted semi-auto dry transfer and fabrication of high- performance monolayer CVD WS2 transistor. In IEEE Symp. VLSI Technology and Circuits 290–291 (IEEE, 2022).

Liu, F. et al. Disassembling 2D van der Waals crystals into macroscopic monolayers and reassembling into artificial lattices. Science 367, 903–906 (2020).

Ghosh, S. et al. Integration of epitaxial monolayer MX2 channels on 300 mm wafers via collective-die-to-wafer (CoD2W) transfer. In 2023 IEEE Symp. VLSI Technology and Circuits https://doi.org/10.23919/VLSITechnologyandCir57934.2023.10185215 (IEEE, 2023).

Mannix, J. et al. Robotic four-dimensional pixel assembly of van der Waals solids. Nat. Nanotechnol. 17, 361–366 (2022).

Schulman, S., Arnold, A. J. & Das, S. Contact engineering for 2D materials and devices. Chem. Soc. Rev. 47, 3037–3058 (2018).

Wang, Y. et al. P-type electrical contacts for 2D transition-metal dichalcogenides. Nature 610, 61–66 (2022).

Kwon et al. Interaction- and defect-free van der Waals contacts between metals and two- dimensional semiconductors. Nat. Electron. 5, 241–247 (2022).

Liu, Y. et al. Approaching the Schottky–Mott limit in van der Waals metal–semiconductor junctions. Nature 557, 696–700 (2018).

Liu et al. Graphene-assisted metal transfer printing for wafer-scale integration of metal electrodes and two-dimensional materials. Nat. Electron. 5, 275–280 (2022).

Wang, J. et al. Steep slope p-type 2D WSe2 field-effect transistors with van der waals contact and negative capacitance. In IEEE Int. Electron Devices Meet. (IEDM) 22.3.1–22.3.4 (IEEE, 2018).

Yang, X. et al. Highly reproducible van der Waals integration of two-dimensional electronics on the wafer scale. Nat. Nanotechnol. 18, 471–478 (2023).

Jung, Y. et al. Transferred via contacts as a platform for ideal two-dimensional transistors. Nat. Electron. 2, 187–194 (2019).

Huang, J.-K. et al. High-κ perovskite membranes as insulators for two-dimensional transistors. Nature 605, 262–267 (2022).

Lu, Z. et al. Wafer-scale high-κ dielectrics for two-dimensional circuits via van der Waals integration. Nat. Commun. 14, 2340 (2023).

Zhang et al. Single-crystalline van der Waals layered dielectric with high dielectric constant. Nat. Mater. 22, 832–837 (2023).

Dolui, I., Rungger, C., Das Pemmaraju & Sanvito, S. Possible doping strategies for MoS2 monolayers: an ab initio study. Phys. Rev. B 88, 075420 (2013).

Chowdhury, S., Venkateswaran, P. & Somvanshi, D. A systematic study on the electronic structure of 3D, 4D, and 5D transition metal-doped WSe2 monolayer. Superlattices Microstruct. 148, 106746 (2020).

Suh et al. Doping against the native propensity of MoS2: degenerate hole doping by cation substitution. Nano Lett. 14, 6976–6982 (2014).

Kozhakhmetov, A. et al. Controllable p-type doping of 2D WSe2 via vanadium substitution. Adv. Funct. Mater. 31, 2105252 (2021).

Zhang, K. et al. Tuning the electronic and photonic properties of monolayer MoS2 via in situ rhenium substitutional doping. Adv. Funct. Mater. 28, 1706950 (2018).

Torsi, R. et al. Dilute rhenium doping and its impact on defects in MoS2. ACS Nano 17, 15629–15640 (2020).

Zhang, L. et al. Tuning electrical conductance in bilayer MoS2 through defect-mediated interlayer chemical bonding. ACS Nano 14, 10265–10275 (2020).

Zou, J. et al. Doping concentration modulation in vanadium-doped monolayer molybdenum disulfide for synaptic transistors. ACS Nano 15, 7340–7347 (2021).

Jiang, J. et al. Probing giant Zeeman shift in vanadium-doped WSe2 via resonant magnetotunneling transport. Phys. Rev. B 103, 014441 (2021).

Li, S. et al. Tunable doping of rhenium and vanadium into transition metal dichalcogenides for two-dimensional electronics. Adv. Sci. 8, e2004438 (2021).

Zhao, Y. et al. Doping, contact and interface engineering of two-dimensional layered transition metal dichalcogenides transistors. Adv. Funct. Mater. 27, 1603484 (2017).

Stesmans, B., Schoenaers & Afanas, V. V. Variations of paramagnetic defects and dopants in geo-MoS2 from diverse localities probed by ESR. J. Chem. Phys. 152, 234702 (2020).

Tan, M. Z., Freysoldt, C. & Hennig, R. G. First-principles investigation of charged dopants and dopant-vacancy defect complexes in monolayer MoS2. Phys. Rev. Mater. 4, 114002 (2020).

Zhang, F. et al. Carbon doping of WS2 monolayers: bandgap reduction and p-type doping transport. Sci. Adv. 5, eaav5003 (2019).

Tang et al. Direct n- to p-type channel conversion in monolayer/few-layer WS2 field- effect transistors by atomic nitrogen treatment. ACS Nano 12, 2506–2513 (2018).

Huang et al. Selective engineering of chalcogen defects in MoS2 by low-energy helium plasma. ACS Appl. Mater. Interf. 11, 24404–24411 (2019).

Luo, P. et al. Doping engineering and functionalization of two-dimensional metal chalcogenides. Nanoscale Horiz. 4, 26–51 (2019).

Zhang, X., Shao, Z., Zhang, X., He, Y. & Jie, J. Surface charge transfer doping of low- dimensional nanostructures toward high-performance nanodevices. Adv. Mater. 28, 10409–10442 (2016).

Arnold, A. J., Schulman, D. S. & Das, S. Thickness trends of electron and hole conduction and contact carrier injection in surface charge transfer doped 2D field effect transistors. ACS Nano 14, 13557–13568 (2020).

Yamamoto, S., Nakaharai, K., Ueno & Tsukagoshi, K. Self-limiting oxides on WSe2 as controlled surface acceptors and low-resistance hole contacts. Nano Lett. 16, 2720–2727 (2016).

McClellan, J., Yalon, E., Smithe, K. K. H., Suryavanshi, S. V. & Pop, E. High current density in monolayer MoS2 doped by AlOx. ACS Nano 15, 1587–1596 (2021).

Rai et al. Air stable doping and intrinsic mobility enhancement in monolayer molybdenum disulfide by amorphous titanium suboxide encapsulation. Nano Lett. 15, 4329–4336 (2015).

Cai, L. et al. Rapid flame synthesis of atomically thin MoO3 down to monolayer thickness for effective hole doping of WSe2. Nano Lett. 17, 3854–3861 (2017).

Chen, K. et al. Air stable n-doping of WSe2 by silicon nitride thin films with tunable fixed charge density. APL Mater. 2, 092504 (2014).

Choi & Lee, J. C. Scaling equivalent oxide thickness with flat band voltage (VFB) modulation using in situ Ti and Hf interposed in a metal/high-κ gate stack. J. Appl. Phys. 108, 064107 (2010).

Lee, H. et al. Dipole doping effect in MoS2 field effect transistors based on phase transition of ferroelectric polymer dopant. Original Res. 10, https://doi.org/10.3389/fmats.2023.1139954 (2023).

Lee et al. Remote modulation doping in van der Waals heterostructure transistors. Nat. Electron. 4, 664–670 (2021).

Wu, X. et al. Dual gate synthetic MoS2 MOSFETs with 4.56µF/cm2 channel capacitance, 320µS/µm Gm and 420 µA/µm Id at 1 V Vd/100 nm Lg. In IEEE Int. Electron Devices Meet. (IEDM) 7.4.1–7.4.4 (IEEE, 2021).

Waltl, M. et al. Perspective of 2D integrated electronic circuits: scientific pipe dream or disruptive technology? Adv. Mater. 34, 2201082 (2022).

Mandyam, S. V., Kim, H. M. & Drndic, M. Large area few-layer TMD film growths and their applications. J. Phys. Mater. 3, 024008 (2010).

Kalanyan et al. Rapid wafer-scale growth of polycrystalline 2H-MoS2 by pulsed metal–organic chemical vapor deposition. Chem. Mater, 29, 6279–6288 (2017).

Amani, M. et al. Growth-substrate induced performance degradation in chemically synthesized monolayer MoS2 field effect transistors. Appl. Phys. Lett. 104, https://doi.org/10.1063/1.4873680 (2014).

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Lau, S. et al. Dielectrics for two-dimensional transition-metal dichalcogenide applications. ACS Nano 17, 9870–9905 (2023).

Illarionov, Y. Y. et al. Insulators for 2D nanoelectronics: the gap to bridge. Nat. Commun. 11, 3385 (2020).

Illarionov, Y. Y. et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. Nat. Electron. 2, 230–235 (2019).

O’Brien, K. P. et al. Process integration and future outlook of 2D transistors. Nat. Commun. 14, 6400 (2023). This article provides an outlook on the future of 2D transistors.

Sebastian, R., Pendurthi, T. H., Choudhury, J. M., Redwing & Das, S. Benchmarking monolayer MoS2 and WS2 field-effect transistors. Nat. Commun. 12, 693 (2021).

Weber, O. et al. High immunity to threshold voltage variability in undoped ultra-thin FDSOI MOSFETs and its physical understanding. In IEEE Int. Electron Devices Meet. https://doi.org/10.1109/IEDM.2008.4796663 (IEEE, 2008).

Bhoir, M. S. et al. Variability sources in nanoscale bulk finFETs and TiTaN — a promising low variability WFM for 7/5 nm CMOS nodes. In IEEE Int. Electron Devices Meet. (IEDM) https://doi.org/10.1109/IEDM19573.2019.8993660 (IEEE, 2019).

Jiang, J., Xu, L., Qiu, C. & Peng, L.-M. Ballistic two-dimensional InSe transistors. Nature 616, 470–475 (2023).

Wang, Y. & Chhowalla, M. Making clean electrical contacts on 2D transition metal dichalcogenides. Nat. Rev. Phys. 4, 101–112 (2022).

Wang, Y. et al. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. Nature 568, 70–74 (2019).

Pang, C.-S. et al. Atomically controlled tunable doping in high-performance WSe2 devices. Adv. Electron. Mater. 6, 1901304 (2020).

Ji, H. G. et al. Chemically tuned p- and n-type WSe2 monolayers with high carrier mobility for advanced electronics. Adv. Mater. 31, 1903613 (2019).

Wu, R. et al. Bilayer tungsten diselenide transistors with on-state currents exceeding 1.5 milliamperes per micrometre. Nat. Electron. 5, 497–504 (2022).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Yu, W. J. et al. Vertically stacked multi-heterostructures of layered materials for logic transistors and complementary inverters. Nat. Mater. 12, 246–252 (2023). This article is the first demonstration of stacked 2D materials for electronics.

Sachid, B. et al. Monolithic 3D CMOS using layered semiconductors. Adv. Mater. 28, 2547–2554 (2016).

Zhou, R. & Appenzeller, J. Three-dimensional integration of multi-channel MoS2 devices for high drive current FETs. In 76th Device Research Conf. (DRC) https://doi.org/10.1109/DRC.2018.8442137 (IEEE, 2018).

Zhao et al. Evaporated tellurium thin films for p-type field-effect transistors and circuits. Nat. Nanotechnol. 15, 53–58 (2020).

Tang, J. et al. Vertical integration of 2D building blocks for all-2D electronics. Adv. Electron. Mater. 6, 2000550 (2020).

Knobloch, T. et al. The performance limits of hexagonal boron nitride as an insulator for scaled CMOS devices based on two-dimensional materials. Nat. Electron. 4, 98–108 (2021).

Xiong, X. et al. Demonstration of vertically-stacked CVD monolayer channels: MoS2 nanosheets GAA-FET with ion > 700 µA/µm and MoS2/WSe2 CFET. In IEEE Int. Electron Devices Meet. (IEDM) 7.5.1–7.5.4 (IEEE, 2021).

Huang, X. et al. Ultrathin multibridge channel transistor enabled by van der Waals assembly. Adv. Mater. 33, 2102201 (2021).

Xia, Y. et al. Wafer-scale demonstration of MBC-FET and C-FET arrays based on two- dimensional semiconductors. Small 18, 2107650 (2022).

Liu, M. et al. Large-scale ultrathin channel nanosheet-stacked CFET based on CVD 1L MoS2/WSe2. Adv. Electron. Mater. 9, 2200722 (2023).

Jia, X. et al. High-performance CMOS inverter array with monolithic 3D architecture based on CVD-grown n-MoS2 and p-MoTe2. Small 19, 2207927 (2023).

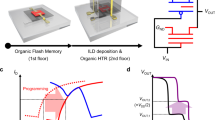

Kang, J. H. et al. Monolithic 3D integration of 2D materials-based electronics towards ultimate edge computing solutions. Nat. Mater. 22, 1470–1477 (2023). This article discusses monolithic 3D integration of 2D materials-based electronics towards ultimate edge computing solutions.

Yang, C.-C. et al. Enabling monolithic 3D image sensor using large-area monolayer transition metal dichalcogenide and logic/memory hybrid 3D+IC. In IEEE Symp. VLSI Technology. https://doi.org/10.1109/VLSIT.2016.7573448 (IEEE, 2016).

Goossens, S. et al. Broadband image sensor array based on graphene–CMOS integration. Nat. Photon. 11, 366–371 (2017).

Wang, C.-H. et al. 3D monolithic stacked 1T1R cells using monolayer MoS2 FET and hBN RRAM fabricated at low (150° C) temperature. In IEEE Int. Electron Devices Meet. (IEDM) 22.5.1–22.5.4 (IEEE, 2018).

Tong, L. et al. Heterogeneous complementary field-effect transistors based on silicon and molybdenum disulfide. Nat. Electron. 6, 37–44 (2023).

Guan, S.-X. et al. Monolithic 3D integration of back-end compatible 2D material FET on Si finFET. npj 2D Mater. Appl. 7, 9 (2023).

Zhu, K. et al. Hybrid 2D–CMOS microchips for memristive applications. Nature 618, 57–62 (2023).

Meng, Y. et al. Photonic van der Waals integration from 2D materials to 3D nanomembranes. Nat. Rev. Mater. 8, 498–517 (2023).

Ko, C.-T. & Chen, K.-N. Low temperature bonding technology for 3D integration. Microelectron. Reliab. 52, 302–311 (2012).

Koneru, A., Kannan, S. & Chakrabarty, K. Impact of electrostatic coupling and wafer-bonding defects on delay testing of monolithic 3D integrated circuits. ACM J. Emerg. Technol. Comput. Syst. 13, (2017).

Chaudhuri, S. et al. Built-in self-test for inter-layer vias in monolithic 3D ICs. In 2019 IEEE Eur. Test Symp. (ETS) https://doi.org/10.1109/ETS.2019.8791515 (IEEE, 2019).

Smets, Q. et al. Sources of variability in scaled MoS2 FETs. In IEEE Int. Electron Devices Meet. (IEDM) 3.1.1–3.1.4 (IEEE, 2020).

Shin, G. et al. Indirect bandgap puddles in monolayer MoS2 by substrate-induced local strain. Adv. Mater. 28, 9378–9384 (2016).

Smithe, K. K. H., Suryavanshi, S. V., Muñoz Rojo, M., Tedjarati, A. D. & Pop, E. Low variability in synthetic monolayer MoS2 devices. ACS Nano 11, 8456–8463 (2017).

Raja et al. Dielectric disorder in two-dimensional materials. Nat. Nanotechnol. 14, 832–837 (2019).

Zantye, B., Kumar, A. & Sikder, A. Chemical mechanical planarization for microelectronics applications. Mater. Sci. Eng. R 45, 89–220 (2004).

Banerjee, G. & Rhoades, R. L. Chemical mechanical planarization historical review and future direction. ECS Trans. 13, https://doi.org/10.1149/1.2912973 (2008).

Das, S. Kibria, G., Doloi, B. & Bhattacharyya, B. Advances in Abrasive Based Machining and Finishing Processes (Springer, 2020).

Zhong, Z.-W. Recent developments and applications of chemical mechanical polishing. Int. J. Adv. Manuf. Technol. 109, 1419–1430 (2020).

Seo, J. A review on chemical and mechanical phenomena at the wafer interface during chemical mechanical planarization. J. Mater. Res. 36, 235–257 (2021).

Zhao, G. et al. Review on modeling and application of chemical mechanical polishing. Nanotechnol. Rev. 9, 182–189 (2020).

Zhao, D. & Lu, X. Chemical mechanical polishing: theory and experiment. Friction 1, 306–326 (2013).

Krishnan, M., Nalaskowski, J. W. & Cook, L. M. Chemical mechanical planarization: slurry chemistry, materials, and mechanisms. Chem. Rev. 110, 178–204 (2010).

Hocheng, Y. L., Huang & Chen, L. J. Kinematic analysis and measurement of temperature rise on a pad in chemical mechanical planarization. J. Electrochem. Soc. 146, 4236 (1999).

White, J., Melvin & Boning, D. Characterization and modeling of dynamic thermal behavior in CMP. J. Electrochem. Soc. 150, G271 (2003).

Oh, S. & Seok, J. Modeling of chemical–mechanical polishing considering thermal coupling effects. Microelectronic Eng. 85, 2191–2201 (2008).

Khursheed, K., Khare & Haque, F. Z. Automation of optimal metal density filling for deep sub-micron technology designs. Mater. Today Proc. 74, 207–212 (2023).

Jiang, B. et al. FIT: fill insertion considering timing. In Proc. 56th Ann. Design Automation Conf. https://doi.org/10.1145/3316781.3317826 (ACM, 2019).

Kahng, B. & Samadi, K. CMP fill synthesis: a survey of recent studies. IEEE Trans. Comput. Des. Integr. Circuits Syst. 27, 3–19 (2008).

Liu, L. et al. A review: green chemical mechanical polishing for metals and brittle wafers. J. Phys. D 54, 373001 (2021).

Sarvar, D. C., Whalley & Conway, P. P. Thermal interface materials — a review of the state of the art. 2006 1st Electron. System Integration Technol. Conf. 2, 1292–1302 (2006).

Lin, S.-C. & Banerjee, K. Thermal challenges of 3D ICs. In Wafer Level 3-D ICs Process Technology (eds Tan, C. S., Gutmann, R. J. & Reif, L. R.) 1–26 (Springer, 2008).

Cahill, G. et al. Nanoscale thermal transport. II. 2003–2012. Appl. Phys. Rev. 1, 011305 (2014).

Liu, X. & Zhang, Y.-W. Thermal properties of transition-metal dichalcogenide. Chin. Phys. B 27, 034402 (2018).

Yalon, E. et al. Energy dissipation in monolayer MoS2 electronics. Nano Lett. 17, 3429–3433 (2017).

Vaziri, S. et al. Ultrahigh thermal isolation across heterogeneously layered two-dimensional materials. Sci. Adv. 5, eaax1325 (2019).

Wang et al. Difference analysis model for the mismatch effect and substrate-induced lattice deformation in atomically thin materials. Phys. Rev. B 98, 245403 (2018).

Zhang & Zhang, Y.-W. Thermal properties of two-dimensional materials. Chin. Phys. B 26, 034401 (2017).

Wang, Y., Xu, N., Li, D. & Zhu, J. Thermal properties of two dimensional layered materials. Adv. Funct. Mater. 27, 1604134 (2017).

Zhong, Y. et al. A unified approach and descriptor for the thermal expansion of two-dimensional transition metal dichalcogenide monolayers. Sci. Adv. 8, eabo3783 (2022).

Kim, S. E. et al. Extremely anisotropic van der Waals thermal conductors. Nature 597, 660–665 (2021).

Fu, Y. et al. Graphene related materials for thermal management. 2D Mater. 7, 012001 (2020).

Ghosh, S. et al. Extremely high thermal conductivity of graphene: prospects for thermal management applications in nanoelectronic circuits. Appl. Phys. Lett. 92, 121911 (2008).

Lee, D., Das, S., Doppa, J. R., Pande, P. P. & Chakrabarty, K. Impa ct of electrostatic coupling on monolithic 3D-enabled network on chip. ACM Trans. Des. Autom. Electron. Syst. 24, (2019).

Xu, C. & Banerjee, K. Physical modeling of the capacitance and capacitive coupling noise of through-oxide vias in FDSOI-based ultra-high density 3-D ICs. IEEE Trans. Electron. Dev. 60, 123–131 (2012).

Batude, P. et al. Advances in 3D CMOS sequential integration. In IEEE Int. Electron Devices Meet. (IEDM) https://doi.org/10.1109/IEDM.2009.5424352 (IEEE, 2009).

Pragathi, D. et al. An extensive survey on reduction of noise coupling in TSV based 3D IC integration. Mater. Today Proc. 45, 1471–1480 (2021).

Kim, S. K., Liu, C. C., Xue, L. & Tiwari, S. Crosstalk reduction in mixed-signal 3-D integrated circuits with interdevice layer ground planes. IEEE Trans. Electron. Dev. 52, 1459–1467 (2005).

Zhu, L. et al. Design automation and test solutions for monolithic 3D ICs. ACM J. Emerg. Technol. Comput. Syst. 18, (2021).

Samal, S. K., Nayak, D., Ichihashi, M. Banna, S. & Lim, S. K. Tier partitioning strategy to mitigate BEOL degradation and cost issues in monolithic 3D ICs. In IEEE/ACM Int. Conf. Computer-Aided Design (ICCAD) https://doi.org/10.1145/2966986.2967080 (ACM, 2016).

Guler & Jha, N. K. Hybrid monolithic 3-D IC floorplanner. IEEE Trans. Very Large Scale Integr. Syst. 26, 1868–1880 (2018).

Berhault, G., Brocard, M., Thuries, S., Galea, F. & Zaourar, L. 3DIP: an iterative partitioning tool for monolithic 3D IC. In IEEE Int. 3D Systems Integration Conf. (3DIC) https://doi.org/10.1109/3DIC.2016.7970013 (IEEE, 2016).

Bamberg, L., García-Ortiz, A., Zhu, L., Pentapati, S. & Lim, S. K. Macro-3D: a physical design methodology for face-to-face-stacked heterogeneous 3D ICs. In Design, Automation & Test in Europe Conf. Exhib. (DATE) 37–42 (IEEE, 2020).

Lu, Y.-C., Pentapati, S. S. K., Zhu, L., Samadi, K. & Lim, S. K. TP-GNN: a graph neural network framework for tier partitioning in monolithic 3D ICs. In 57th ACM/IEEE Design Automation Conf. (DAC) https://doi.org/10.1109/DAC18072.2020.9218582 (IEEE, 2020).

Chang, K. et al. Cascade2D: a design-aware partitioning approach to monolithic 3D IC with 2D commercial tools. In IEEE/ACM Int. Conf. Computer-Aided Design (ICCAD) https://doi.org/10.1145/2966986.2967013 (ACM, 2020).

Panth, S., Samadi, K., Du, Y. & Lim, S. K. Shrunk-2-D: a physical design methodology to build commercial-quality monolithic 3-D ICs. IEEE Trans. Comput. Des. Integr. Circuits Syst. 36, 1716–1724 (2017).

Ku, W., Chang, K. & Lim, S. K. Compact-2D: a physical design methodology to build two- tier gate-level 3-D ICs. IEEE Trans. Comput. Des. Integr. Circuits Syst. 39, 1151–1164 (2019).

Cong, J. & Luo, G. A multilevel analytical placement for 3D ICs. In Asia and South Pacific Design Automation Conf. 361–366 (IEEE, 2009).

Hsu, M.-K., Chang, Y.-W. & Balabanov, V. TSV-aware analytical placement for 3D IC designs. In Proc. 48th Design Automation Conf. 664–669 (2011).

Lu, J., Zhuang, H., Kang, I., Chen, P. & Cheng, C.-K. ePlace-3D: electrostatics based placement for 3D-ICs. In Proc. 2016 Int. Symp. Physical Design (ISPD ’16) 11–18 (ACM, 2016).

Minz, J., Zhao, X. & Lim, S. K. Buffered clock tree synthesis for 3D ICs under thermal variations. In Asia and South Pacific Design Automation Conf. 504–509 (IEEE, 2008).

Campregher, N., Cheung, P. Y., Constantinides, G. A. & Vasilko, M. Analysis of yield loss due to random photolithographic defects in the interconnect structure of FPGAs. In Proc. 2005 ACM/SIGDA 13th Int. Symp. Field-Programmable Gate Arrays 138–148 (2005).

Patterson, D., Wildman, H., Gal, D. & Wu, K. Detection of resistive shorts and opens using voltage contrast inspection. In 17th Ann. SEMI/IEEE ASMC 2006 Conf. 327–333 (IEEE, 2006).

Bernardi, P., Sonza Reorda, M., Bosio, A., Girard, P. & Pravossoudovitch, S. On the modeling of gate delay faults by means of transition delay faults. In 2011 IEEE Int. Symp. on Defect and Fault Tolerance in VLSI and Nanotechnology Systems 226–232 (IEEE, 2011).

Pomeranz & Reddy, S. M. Transition path delay faults: a new path delay fault model for small and large delay defects. IEEE Trans. VLSI Syst. 16, 98–107 (2007).

Erb, D., Scheibler, K., Sauer, M., Reddy, S. M. & Becker, B. Multi-cycle circuit parameter independent ATPG for interconnect open defects. In IEEE 33rd VLSI Test Symp. (VTS) https://doi.org/10.1109/VTS.2015.7116296 (IEEE, 2015).

Koneru, A., Kannan, S. & Chakrabarty, K. A design-for-test solution based on dedicated test layers and test scheduling for monolithic 3-D integrated circuits. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 38, 1942–1955 (2018).

Jayachandran, D. et al. Three-dimensional integration of two-dimensional field-effect transistors. Nature 625, 276–281 (2024). This article demonstrates large-scale 3D integration of 2D FETs.

Dorow, J. et al. Gate length scaling beyond Si: mono-layer 2D channel FETs robust to short channel effects. In IEEE Int. Electron Devices Meet. (IEDM) 7.5.1–7.5.4 (IEEE, 2022).

Cheng, C. C. et al. First demonstration of 40-nm channel length top-gate WS2 pFET using channel area-selective CVD growth directly on SiOx/Si substrate. In 2019 Symp. VLSI Technology T244–T245 (2019).

Chou, A.-S. et al. High on-current 2D nFET of 390 μA/μm at VDS = 1 V using monolayer CVD MoS2 without intentional doping. In IEEE Symp. VLSI Technology https://doi.org/10.1109/VLSITechnology18217.2020.9265040 (IEEE, 2020).

Chou, A.-S. et al. Antimony semimetal contact with enhanced thermal stability for high performance 2D electronics. In IEEE Int. Electron Devices Meet. (IEDM) 7.2.1–7.2.4 (IEEE, 2021).

Sathaiya, M. et al. Comprehensive physics based TCAD model for 2D MX2 channel transistors. In IEEE Int. Electron Devices Meet. (IEDM) 28.4.1–28.4.4 (IEEE, 2022).

Su, S. K. et al. Perspective on low-dimensional channel materials for extremely scaled CMOS. In IEEE Symp. VLSI Technology and Circuits 403–404 (IEEE, 2022).

Chou, A. S. et al. High-performance monolayer WSe2 p/n FETs via antimony-platinum modulated contact technology towards 2D CMOS electronics. In Int. Electron Devices Meet. (IEDM) https://doi.org/10.1109/IEDM45625.2022.10019491 (IEEE, 2022).

Wu, W. C. et al. Scaled contact length with low contact resistance in monolayer 2D channel transistors. In IEEE Symp. VLSI Technology and Circuits https://doi.org/10.23919/VLSITechnologyandCir57934.2023.10185408 (IEEE, 2023).

Dorow, J. et al. Advancing monolayer 2D NMOS and PMOS transistor integration from growth to van der Waals interface engineering for ultimate CMOS scaling. In Symp. VLSI Technology 1–2 (IEEE, 2021).

Maxey, K. et al. 300 mm MOCVD 2D CMOS materials for more (than) Moore scaling. In IEEE Symp. VLSI Technology and Circuits 419–420 (IEEE, 2022).

Naylor, H. et al. 2D Materials in the BEOL. In IEEE Symp. VLSI Technology and Circuits https://doi.org/10.23919/VLSITechnologyandCir57934.2023.10185307 (IEEE, 2023).

Schram, T. et al. High yield and process uniformity for 300 mm integrated WS2 FETs. In Symp. VLSI Technology 1–2 (2021).

Smets, Q. et al. Scaling of double-gated WS2 FETs to sub-5nm physical gate length fabricated in a 300 mm FAB. In IEEE Int. Electron Devices Meet. (IEDM) 34.2.1–34.2.4 (IEEE, 2021).

Brems, S. et al. Overview of scalable transfer approaches to enable epitaxial 2D material integration. In Int. VLSI Symp. Technology, Systems and Applications (VLSI-TSA/VLSI-DAT) 1–2 (2023).

Author information

Authors and Affiliations

Contributions

S.D. conceptualized this work and secured resources. D.J. and N.U.S. researched data for the article, structured and wrote the manuscript. D.J., N.U.S. and S.D. reviewed the manuscript before submission.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Reviews Electrical Engineering thanks the anonymous reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Related links

2DFactory: https://www.2dfactory.com/

AIXTRON: https://www.aixtron.com/en

Graphenea: https://www.graphenea.com/

Veeco: https://www.veeco.com/

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Jayachandran, D., Sakib, N.U. & Das, S. 3D integration of 2D electronics. Nat Rev Electr Eng (2024). https://doi.org/10.1038/s44287-024-00038-5

Accepted:

Published:

DOI: https://doi.org/10.1038/s44287-024-00038-5