# scientific reports

### OPEN

Check for updates

## Floating body effect in indium–gallium–zinc–oxide (IGZO) thin-film transistor (TFT)

Jingyu Park<sup>1,4</sup>, Seungwon Go<sup>2,4</sup>, Woojun Chae<sup>3</sup>, Chang Il Ryoo<sup>3</sup>, Changwook Kim<sup>1</sup>, Hyungju Noh<sup>2</sup>, Seonggeun Kim<sup>2</sup>, Byung Du Ahn<sup>3</sup>, In-Tak Cho<sup>3</sup>, Pil Sang Yun<sup>3</sup>, Jong Uk Bae<sup>3</sup>, Yoo Seok Park<sup>3</sup>, Sangwan Kim<sup>2⊠</sup> & Dae Hwan Kim<sup>1⊠</sup>

In this paper, the floating body effect (FBE) in indium-gallium-zinc-oxide (IGZO) thin-film transistor (TFT) and the mechanism of device failure caused by that are reported for the first time. If the toggle AC pulses are applied to the gate and drain simultaneously for the switching operation, the drain current of IGZO TFT increases dramatically and cannot show the on/off switching characteristics. This phenomenon was not reported before, and our study reveals that the main cause is the formation of a conductive path between the source and drain: short failure. It is attributed in part to the donor creation at the drain region during the high voltage ( $V_{high}$ ) condition and in part to the donor creation at the source region during the falling edge and low voltage (V<sub>low</sub>) conditions. Donor creation is attributed to the peroxide formation in the IGZO layer induced by the electrons under the high lateral field. Because the donor creation features positive charges, it lowers the threshold voltage of IGZO TFT. In detail, during the  $V_{high}$  condition, the donor creation is generated by accumulated electrons with a high lateral field at the drain region. On the other hand, the floating electrons remaining at the short falling edge (i.e., FBE of the IGZO TFT) are affected by the high lateral field at the source region during the V<sub>low</sub> condition. As a result, the donor creation is generated at the source region. Therefore, the short failure occurs because the donor creations are generated and expanded to channel from the drain and source region as the AC stress accumulates. In summary, the FBE in IGZO TFT is reported, and its effect on the electrical characteristics of IGZOTFT (i.e., the short failure) is rigorously analyzed for the first time.

An amorphous indium-gallium-zinc-oxide (IGZO) thin-film transistor (TFT) has been widely used in the field of high-performance display and complementary metal–oxide–semiconductor (CMOS) back-end-of-line (BEOL) circuits due to its high mobility (>10 cm<sup>2</sup>/V s), ultra-low leakage current, large on/off current ratio, large-area uniformity, low cost and low-temperature process<sup>1–7</sup>. Despite these advantages, the IGZO TFT has suffered from several technical issues, such as the development of p-type semiconductor<sup>8</sup>, bias instability (i.e., DC and AC stresses)<sup>9–16</sup> and reliability problems related to the oxygen vacancy<sup>17,18</sup>, excessive oxygen<sup>19,20</sup>, and metal cation<sup>21</sup>. Therefore, many research groups have been studied for the reliability of IGZO TFT<sup>8–21</sup>.

In this study, the floating body effect (FBE) in IGZO TFT and device failure due to FBE are reported for the first time. In addition, the mechanism and physics are compared with the FBE in silicon-on-insulator (SOI) metal-oxide-semiconductor field-effect transistor (MOSFET)<sup>22–24</sup>. In the case of n-channel SOI MOSFET, the electron-hole pairs (EHPs) are generated by impact ionization as the high electric field is induced at channel-drain junction during the saturation mode [i.e., the high gate voltage ( $V_{\rm GS}$ ) and drain voltage ( $V_{\rm DS}$ )]. The electrons can move toward the drain electrode while the holes are accumulated at the floating body. The accumulated holes increase the body potential, which lowers the threshold voltage ( $V_{\rm th}$ ) and increases the drain current ( $I_{\rm D}$ ). Therefore, the stored holes at the floating body cause the degradation of the device and/or circuit reliability, such as the history effect, propagation delay, and so on<sup>22–27</sup>.

On the other hand, it is well known that FBE rarely occurs in the IGZO TFT because it features intrinsic n-type and low impact ionization generation rate due to a large bandgap ( $E_g > 3 \text{ eV}$ )<sup>28–30</sup>. However, the IGZO TFT is mainly used for the gate driver in display applications, which requires a higher supply voltage than CMOS

<sup>1</sup>School of Electrical Engineering, Kookmin University, Seoul 02707, Republic of Korea. <sup>2</sup>Department of Electronic Engineering, Sogang University, Seoul 04107, Republic of Korea. <sup>3</sup>Large Display Business Unit, LG Display Company, Paju 10845, Republic of Korea. <sup>4</sup>These authors contributed equally: Jingyu Park and Seungwon Go. <sup>⊠</sup>email: sangwan@sogang.ac.kr; drlife@kookmin.ac.kr

logic. Furthermore, it is vulnerable to FBE regarding circuit topology because the driver usually uses a gateddiode structure (i.e., synchronized gate and drain)<sup>31-34</sup>.

In this study, the FBE in IGZO TFT, which occurs when the AC pulse is applied for gated-diode operation, is reported for the first time, and the mechanism is analyzed. This paper is organized as follows. First, the fabricated device structure and measurement method are explained. Next, the electrical characteristics of IGZO TFTs are demonstrated, and their degradation mechanism due to FBE is proposed. After the mechanism is examined by the technology computer-aided design (TCAD) simulation, the FBE in IGZO TFT is compared with that in SOI MOSFET for precise analysis.

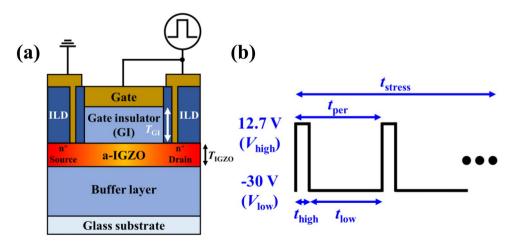

#### Device fabrication and measurement method

Figure 1a shows the schematic of the IGZO TFT with a self-aligned top gate structure. The channel length and width were 6 and 250  $\mu$ m, respectively. After depositing a 300 nm-thick SiO<sub>2</sub> buffer layer on the glass substrate by using plasma-enhanced chemical vapor deposition (PECVD), a 30 nm-thick amorphous IGZO channel (In:Ga:Zn = 1:1:1 mol%) was deposited by DC sputtering. The 150 nm-thick SiO<sub>2</sub> gate oxide and Cu/MoTi gate were deposited by PECVD and DC sputtering, respectively. After gate patterning, the plasma treatment was performed for the highly conductive source/drain region<sup>35</sup>. Subsequently, the interlayer dielectric (ILD) was deposited and patterned for the source/drain region. The source/drain electrodes were formed by Cu/MoTi.

The gated diode (i.e., synchronized gate and drain) IGZO TFT is usually used as a switching device in the gate driver circuit and transmits the image signal to the pixel circuit. Therefore, the electrical characteristics were investigated after applying toggle pulses to examine the switching application. As shown in Fig. 1b, the switching pulses were composed of 12.7 V-high voltage ( $V_{high}$ ) and -30 V-low voltage ( $V_{low}$ ) and applied to the gate and drain simultaneously (Fig. 1a). In addition, the pulse was set to 16.6% duty cycle with 30 ms period (i.e., the pulse with 5 ms of  $V_{high}$  and 25 ms of  $V_{low}$ ) and 100 ns of rising/falling time.

#### **Results and discussion**

#### Electrical characteristics and degradation mechanism of IGZO TFT with AC pulse

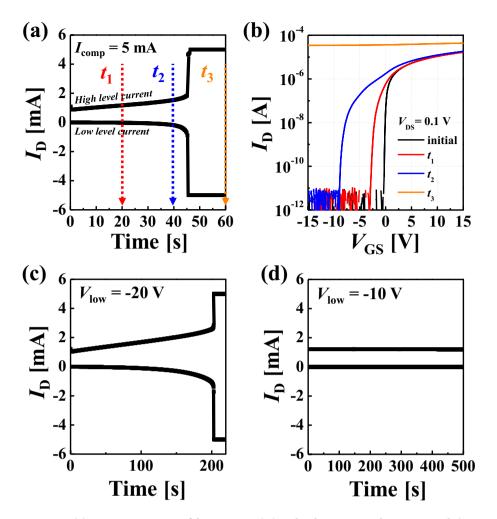

Figure 2a shows the drain current  $(I_D)$  under the AC pulse stress in Fig. 1b. Because a period of pulse is 30 ms, the stress time 20 s  $(t_1)$ , 40 s  $(t_2)$ , and 60 s  $(t_3)$  are corresponded to 666, 1333, and 2000 pulse stress, respectively. As the stress time increases, the  $I_D$  increases gradually. It is attributed to the decrease of  $V_{th}$  (Fig. 2b). Generally, these phenomena can be explained by the donor creation at the channel adjacent to the drain region<sup>11,12,36</sup>. The origin of donor creation in IGZO is well known as the formation of peroxide (i.e.,  $O^{2-} + O^{2-} \rightarrow O_2^{2-} + 2e^{-}$ ) when the strong electric field is applied to the large amount of electrons<sup>19,20</sup>. In detail, if the IGZO TFT is fully turned on (i.e., strong accumulation at  $V_{GS} = V_{high}$ ) and large  $V_{DS}$  is applied, the high lateral electric field is applied at the channel-drain junction with high electron concentration at the channel. It can be confirmed that the extracted subgap density-of-state (DOS) [g(e)] increases after stress, corresponding to the generation of donor creation, as shown in Figure S1. As a result, there are donor creations, and the increment of carrier concentration lowers  $V_{th}$ .

The interesting point is that the  $I_D$  rapidly increases to the compliance current after 45 s (Fig. 2a) and cannot show on/off switching characteristics (Fig. 2b,  $t_3$ ). The detailed images for the short failure are described in the supplementary information (including Figure S2). It is analyzed by the short failure between the source and drain, not the gate leakage current (Figure S3). However, the short failure cannot be explained by the abovementioned donor creation because it is locally generated at the channel adjacent to the drain. In addition, the degradation is affected by the amplitude of  $V_{low^2}$  as shown in Fig. 2a, c, and d. In detail, the short failure occurs after 45 s and 200 s with -30 V and -20 V- $V_{low^2}$  respectively, while there is no failure with -10 V- $V_{low}$  until 500 s stress time. In other words, the required number of stress pulses (i.e., the stress time) is increased with the smaller  $V_{low^2}$ However, the result cannot be explained by the donor creation at the drain region because the electric field at the drain is rarely affected by the amplitude of  $V_{low^2}$ .

Figure 1. Schematics of (a) IGZO TFT and (b) synchronized gate and drain AC pulse.

**Figure 2.** (a) Transient response of drain current ( $I_D$ ) under the AC stress shown in Fig. 1b (i.e.,  $V_{high} = 12.7 \text{ V}$  and  $V_{low} = -30 \text{ V}$ ). Here, the high level and low level current are measured during  $V_{high}$  and  $V_{low}$ , respectively. (b) Transfer curves before and after AC stress pulses are applied to the IGZO TFT. Transient response of  $I_D$  under the AC stress with the different  $V_{low}$  from (a); (c)  $V_{low} = -20 \text{ V}$  and (d)  $V_{low} = -10 \text{ V}$ .

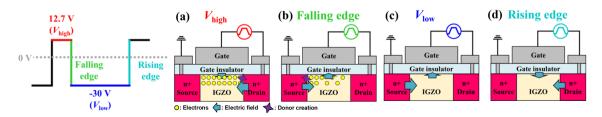

Our group hypothesizes that there are different degradation mechanisms depending on the segment of AC pulse applied to the gate and drain simultaneously (Fig. 3). First, in the case of  $V_{high}$  (Fig. 3a), the electrons at the channel are affected by a high lateral electric field, especially around the drain region due to the large  $V_{DS}$ . As a result, the donor creation occurs at the drain region, as discussed before. Second, a number of accumulated electrons remains without recombination during the 100 ns falling edge (i.e., the transition from  $V_{high}$  to  $V_{low}$ ) because the lifetime of electrons in IGZO is ~  $\mu s^{37-39}$ . At the same time, the electric field at the source is significantly increased when the applied voltage decreases from 0 V to  $V_{low}$ . As a result, the donor creation occurs at the floating body are affected by the strong lateral electric field at the source region. This phenomenon (i.e., the donor creation at the source during the falling edge) is defined as the FBE in IGZO TFT and analyzed in detail (will be discussed later). Third, in the  $V_{low}$  condition (Fig. 3c), although the lateral electric field is high enough, there is no donor creation because most of the electrons are recombined. Similarly, there are not enough electrons during the rising edge (i.e., the transition from  $V_{low}$  to

**Figure 3.** Degradation mechanism of IGZO TFT during AC pulse stress under (a)  $V_{\text{high}}$ , (b) falling edge, (c)  $V_{\text{low}}$  and (d) rising edge conditions.

$V_{\rm high}$ ) for the donor creation (Fig. 3d). In summary, if the gated-diode operation is repeated (i.e., synchronized AC pulses are applied to the gate and drain repeatedly), the donor creation occurs at the drain during the  $V_{\rm high}$  condition due to the accumulated electrons. In contrast, the FBE-induced donor creation occurs at the source during the falling edge due to the floating electrons.

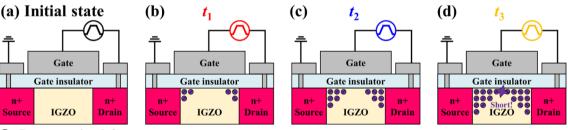

Figure 4 shows the short failure steps in IGZO TFT (Fig. 2b,  $t_3$ ) according to the number of the applied AC pulses. As mentioned above, the donor creation is generated at the drain and source during  $V_{high}$  (Fig. 3a) and falling edge (Fig. 3b), respectively. Moreover, the donor creation is accumulated as the number of AC pulses increases. In the early stage of stress (Fig. 4b), the  $V_{th}$  is decreased due to the increase of channel potential (Fig. 2b,  $t_1$ ). As the number of applied pulses increases, the donor creation region gradually expands from the drain and source to the channel, resulting in a decrease in the effective channel length (Fig. 4c). Finally, as shown in Fig. 4d, the donor creation occurs in most channel regions. It results in short failure (channel cannot be OFF despite  $V_{low}$ ), and the switching application of IGZO TFT is impossible (Fig. 2a and b,  $t_4$ ). It is clear that the phenomena, which cannot be explained by the donor creation of the donor creation at the drain region, can be well explained by the proposed FBE-induced donor creation (for evidence of the generation of the donor creation at the drain/source region and the short failure, see the Supplementary Information, Figure S4). The critical point of the proposed degradation mechanism is that the electrons cannot be recombined during the falling edge (i.e., the FBE in IGZO TFT).

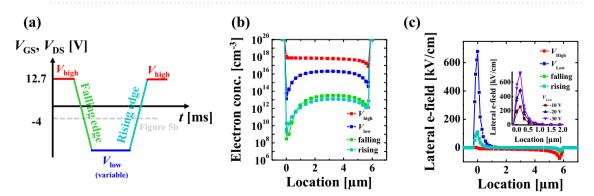

#### TCAD simulation of the FBE in IGZO TFT

The mixed-mode TCAD simulation is performed to verify the proposed degradation mechanism, the FBE in IGZO TFT. The parameter of DOS is extracted and adapted to the IGZO layer for precise simulation (Table S1). More details about the TCAD simulation are described in the supplementary. The AC pulse is set as in Fig. 5a, and the distribution of electron concentration and electric field along the channel are extracted at  $V_{high}$ ,  $V_{low}$  falling, and rising edges. The falling and rising edges are defined when the AC pulse is -4 V as shown in the gray dot line in Fig. 5a. As shown in Fig. 5b, the electron concentration at the falling edge and at the rising edge, the former is much larger than the latter. In other words, it is confirmed a large number of floating electrons remain without recombination during the falling edge. At the same time, Fig. 5c shows the electric field at the source region is significant in order of the  $V_{low}$ , falling/rising edges, and  $V_{high}$ . As a result, during the falling edge, the floating electrons at the channel are affected by the high lateral electric field, generating the donor creation at the channel adjacent to the source region. Furthermore, the inset of Fig. 5c shows that the electric field decreases as the  $V_{low}$  lowers, which is well corresponds to the tendency of short failure with the various amplitudes of the  $V_{low}$  (Fig. 2a,c, and d). In conclusion, the short failure in IGZO TFT is attributed in part to the donor creation at the drain region during  $V_{high}$  and in part to the FBE-induced donor creation at the source region during the falling edge.

S: Donor creation defects

**Figure 4.** Schematic of short fail mechanism during ac stress with (a) initial condition and after (b)  $t_1$ , (c)  $t_2$ , and (d)  $t_3$  in Fig. 2a.

**Figure 5.** (a) Mixed-mode TCAD simulation pulse setup, (b) electron concentration distribution with  $-30 \text{ V-}V_{\text{low}}$  and (c) electric field distribution at  $V_{\text{high}}$ ,  $V_{\text{low}}$ , and falling/rising edges in channel region along to source-drain direction. The inset of (c) shows the electric field with the different  $V_{\text{low}}$ , which corresponds to Fig. 2a,b, and c; -30 V (purple), -20 V (navy), -10 V (wine).

#### Comparison between the FBEs in IGZO TFT and SOI MOSFET

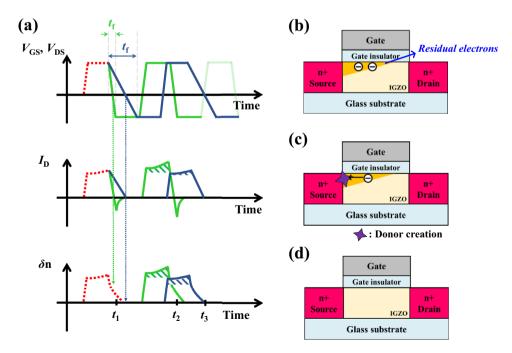

In this section, the FBEs in IGZO TFT and SOI MOSFET are compared for precise analysis. Figure 6a shows the schematics of  $V_{GS}$ ,  $V_{DS}$ ,  $I_D$ , and electron concentration of IGZO TFT with the initial and subsequent AC pulses. As discussed in the previous section, the FBE-induced donor creation can be generated if the high lateral electric field is applied to the floating electrons, which are generated at  $V_{GS} = V_{DS} = V_{high}$  and cannot be recombined during the falling edge because their lifetime is more prolonged than  $V_{high}$  to  $V_{low}$  transition time (Fig. 6b; FBE in IGZO TFT). Therefore, the transient time from  $V_{high}$  to  $V_{low}$  at the falling edge and the amplitude of the  $V_{low}$  (i.e., lateral electric field) are the most significant factors for FBE in IGZO TFT. In the case of short  $t_f$  (green line), there is donor creation because the floating electrons are affected by the high lateral electric field (Fig. 6c). The donor creation makes  $V_{th}$  decrease (Fig. 2b), and hence, the  $I_D$  during the following pulse is more significant than that for the initial pulse. As a result, more floating electrons are generated/accumulated in the channel, and FBE is accelerated. On the contrary, if the falling edge time ( $t_f$ ) is longer than the electron lifetime (indigo line, Fig. 6d), the FBE-induced donor creation cannot be generated because most of the electrons are recombined, and hence, there are not enough electrons when the source lateral electric field is increased (i.e.,  $V_{GS}$  and  $V_{DS}$  change from 0 V to  $V_{low}$ ;  $t_{f,low}$ ). Therefore, it shows the same results for the initial and following pulses regarding  $I_D$  and electron concentration.

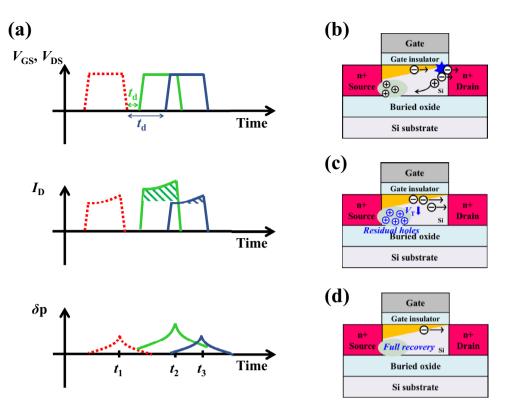

On the other hand, as shown in Fig. 7a, the FBE in SOI MOSFET is defined as the decrease of  $V_{th}$  due to the accumulated holes at the floating body in the saturation operation (i.e.,  $V_{high}$ ). Compared with FBE in IGZO TFT, the accumulation of carriers in the floating body is very similar (Fig. 7b). However, unlike the IGZO TFT, the accumulated holes in SOI MOSFET directly influence the device performance,  $V_{th}$  shift. Therefore, the FBE is more affected by the delay time ( $t_d$ ; the time between the initial pulse and the following pulse), which determines the recombination rate of the floating holes rather than  $t_f$ . In the case of short  $t_d$  (green line, Fig. 7c), the overdrive voltage (i.e.,  $V_{GS}$ - $V_{th}$ ) increases during the following pulse since the floating holes lower  $V_{th}$ . As a result, despite the same bias condition, the larger  $I_D$  generates larger excess holes due to impact ionization, and there is positive feedback regarding  $I_D$  and floating holes. In contrast, if  $t_d$  is longer than the lifetime of floating holes (indigo line, Fig. 7d), the SOI MOSFET under the following pulse is in the same state as that under the initial pulse because all floating holes are recombined.

Consequently, the FBEs in IGZO TFT and SOI MOSFET are similar because the accumulated carriers in the floating body influence the following pulse in both cases. However, there are main differences in terms of the way that the floating carriers impact the device characteristics. In detail, the floating electrons in IGZO TFT induce the donor creation if there is a sufficient lateral electric field. At the same time, the floating holes directly change body potential and  $V_{th}$  in SOI MOSFET. Therefore, the dominant factors for FBEs are  $t_d$  in SOI MOSFET and  $t_f$  in IGZO TFT, respectively. It is noteworthy that the energy bandgap of IGZO is about three times larger than that of Si. Therefore, there are a tiny number of holes in IGZO, and the electron lifetime is much longer than that for Si. In addition, the FBE in SOI MOSFET can be suppressed by adjusting the doping concentration and by using trap engineering<sup>40–44</sup>. However, in the case of IGZO TFT, only a limited range of doping concentration

**Figure 6.** The schematics of (**a**) bias condition ( $V_{GS}$  and  $V_{DS}$ ),  $I_D$ , and electron concentration of IGZO TFT with initial pulse and the next pulse applied with short falling time (green line) and long falling time (indigo line), (**b**) FBE in IGZO TFT at the  $t_1$  (i.e.,  $V_{GS}$  and  $V_{DS}$  change from  $V_{high}$  to 0 V;  $t_{f,high}$ ) which occurs regardless of falling time. The schematics of IGZO TFT during the (**c**) short falling time ( $t_2$ ) and (**d**) long falling time ( $t_3$ ).

**Figure 7.** The schematics of (**a**) bias condition ( $V_{GS}$  and  $V_{DS}$ ),  $I_D$ , and hole concentration of SOI MOSFET with the initial pulse and the next pulse applied with short delay time (green line) and long delay time (indigo line), (**b**) FBE in SOI MOSFET at the  $t_1$  which occurs regardless of delay time. The schematics of SOI MOSFET during the (**c**) short delay time ( $t_2$ ) and (**d**) long delay time ( $t_3$ ).

is allowed<sup>45,46</sup>, and trap engineering is complex to use due to the amorphous active film structure<sup>47,48</sup>. In conclusion, even though IGZO TFT is more robust than SOI MOSFET in impact ionization, it can be more vulnerable to FBE depending on circuit operating conditions and results in short failure.

#### Conclusion

In this study, the FBE in IGZO TFT is reported for the first time, and the effect on the device characteristics is investigated. If the AC pulse is applied to the gate and drain simultaneously for switching operation, the donor creation at drain region during the  $V_{\text{high}}$  condition and the FBE-induced donor creation at the source region should be considered during the falling edge. In detail, the floating electrons at the channel adjacent to the source region are accelerated and activate the peroxide formation if the transition time from  $V_{\text{high}}$  to  $V_{\text{low}}$  is fast enough. Therefore, the short failure occurs as the AC pulse is applied to the gated diode IGZO TFT (i.e., synchronized gate and drain) because the donor creation at the drain and source regions are generated simultaneously and expanded to the channel. Therefore, the FBE reported for the first time in this manuscript must be considered for reliable signal transmission between the gate driver circuits and pixel circuits.

#### Data availability

The datasets used and/or analysed during the current study available from the corresponding author on reasonable request.

Received: 15 February 2024; Accepted: 21 April 2024 Published online: 02 May 2024

#### References

- Mo, Y. G. et al. Amorphous oxide TFT backplane for large size AMOLED TVs. J. Soc. Inf. Display 19, 19–20. https://doi.org/10. 1889/JSID19.1.16 (2011).

- Nag, M. *et al.* Characteristics improvement of top-gate self-aligned amorphous indium gallium zinc oxide thin-film transistors using a dualgate control. *J. Soc. Inf. Display* 25, 349–355. https://doi.org/10.1002/jsid.558 (2017).

- Noh, J. Y., Han, D. M., Jeong, W. C., Kim, J. W. & Cha, S. Y. 21–1: Development of 55' 4K UHD OLED TV employing the internal gate IC with high reliability and short channel IGZO TFTs. SID Symp. Dig. Tech. Pap. 48, 288–290. https://doi.org/10.1002/sdtp. 11605 (2017).

- Park, J. C., Lee, H.-N. & Im, S. Self-aligned top-gate amorphous indium zinc oxide thin-film transistors exceeding low-temperature poly-Si transistor performance. ACS Appl. Mater. Interfaces 5, 6990–6995. https://doi.org/10.1021/am401128p (2013).

- Geng, D., Kang, D. H., Seok, M. J., Mativenga, M. & Jang, J. High-speed and low-voltage-driven shift register with self-aligned coplanar a-IGZO TFTs. *IEEE Electron Device Lett.* 33, 1012–1014. https://doi.org/10.1109/LED.2012.2194133 (2012).

- Morosawa, N. et al. High-mobility self-aligned top-gate oxide TFT for high-resolution AM-OLED. J. Soc. Inf. Display 21, 467–473. https://doi.org/10.1002/jsid.206 (2013).

- Jang, Y. H. et al. 7–4: Invited paper: Internal compensation type OLED display using high mobility oxide TFT. SID Symp. Dig. Tech. Pap. 48, 76–79. https://doi.org/10.1002/sdtp.11567 (2017).

- Kamiya, T., Nomura, K. & Hosono, H. Present status of amorphous In-Ga-Zn-O thin-film transistors. *Sci. Technol. Adv. Mater.* 11, 044305. https://doi.org/10.1088/1468-6996/11/4/044305 (2010).

- Lee, H.-J., Cho, S. H., Abe, K., Lee, M.-J. & Jung, M. Impact of transient currents caused by alternating drain stress in oxide semiconductors. Sci. Rep. 7, 9782–9790. https://doi.org/10.1038/s41598-017-10285-2 (2017).

- Choi, S. et al. A study on the degradation of In-Ga–Zn-O thin-film transistors under current stress by local variations in density of states and trapped charge distribution. *IEEE Electron Device Lett.* 36, 690–692. https://doi.org/10.1109/LED.2015.2438333 (2015).

- Choi, S. *et al.* The effect of gate and drain fields on the competition between donor-like state creation and local electron trapping in In-Ga-Zn-O thin film transistors under current stress. *IEEE Electron Device Lett.* 36, 1336–1339. https://doi.org/10.1109/LED. 2015.2487370 (2015).

- Kim, J.-H. *et al.* Analysis of threshold voltage shift for full V<sub>GS</sub>/V<sub>DS</sub>/Oxygen-content span under positive bias stress in bottomgate amorphous InGaZnO thin-film transistors. *Micromachines* 12, 327. https://doi.org/10.3390/mi12030327 (2021).

- Zhang, Y., Xie, H. & Dong, C. Electrical performance and bias-stress stability of amorphous InGaZnO thin-film transistors with buried-channel layers. *Micromachines* 10, 779. https://doi.org/10.3390/mi10110779 (2019).

- 14. Choi, S. *et al.* Influence of the gate/drain voltage configuration on the current stress instability in amorphous indium-zinc-oxide thin film transistors with self-aligned top-gate structure. *IEEE Electron Device Lett.* **40**, 1431–1434. https://doi.org/10.1109/LED. 2019.2927378 (2019).

- Choi, S. et al. Positive bias stress instability of InGaZnO TFTs with self-aligned top-gate structure in the threshold-voltage compensated pixel. IEEE Electron Device Lett. 41, 50–53. https://doi.org/10.1109/LED.2019.2954543 (2020).

- Wang, H., Wang, M., Zhang, D. & Shan, Q. Degradation of a-InGaZnO TFTs under synchronized gate and drain voltage pulses. IEEE Trans. Electron Devices 65, 995–1001. https://doi.org/10.1109/TED.2018.2794416 (2018).

- 17. Raja, J. *et al.* Negative gate-bias temperature stability of N-doped InGaZnO active-layer thin-film transistors. *Appl. Phys. Lett.* **102**, 083505. https://doi.org/10.1063/1.4793535 (2013).

- Ryu, B., Noh, H. K., Choi, E. A. & Chang, K. J. O-vacancy as the origin of negative bias illumination stress instability in amorphous In–Ga–Zn–O thin film transistors. *Appl. Phys. Lett.* 97, 022108. https://doi.org/10.1063/1.3464964 (2010).

- Choi, S. *et al.* Excessive oxygen peroxide model-based analysis of positive-bias-stress and negative-bias-illumination-stress instabilities in self-aligned top-gate coplanar in-Ga-Zn-O thin-film transistors. *Adv. Electron. Mater.* 8, 2101062. https://doi.org/10. 1002/aelm.202101062 (2022).

- Choi, S. et al. Effect of oxygen content on current stress-induced instability in bottom-gate amorphous InGaZnO thin-film transistors. Materials 12, 3149. https://doi.org/10.3390/ma12193149 (2019).

- Jang, J. T. *et al.* Cation composition-dependent device performance and positive bias instability of self-aligned oxide semiconductor thin-film transistors: Including oxygen and hydrogen effect. ACS Appl. Mater. Interfaces 14, 1389–1396. https://doi.org/10.1021/ acsami.1c18890 (2022).

- Wei, A., Sherony, M. J. & Antoniadis, D. A. Effect of floating-body charge on SOI MOSFET design. *IEEE Trans. Electron Devices* 45, 430–438. https://doi.org/10.1109/16.658677 (1998).

- Adam, A. O., Higashi, K. & Fukushima, Y. Analytical threshold voltage model for ultra-thin SOI MOSFETs including short-channel and floating body effects. *IEEE Trans. Electron Devices* 46, 729–737. https://doi.org/10.1109/16.753707 (1999).

- Chan, M. et al. Modeling the floating-body effects of fully depleted, partially depleted, and body-grounded SOI MOSFETs. Solid State Electron. 48, 969–978. https://doi.org/10.1016/j.sse.2003.12.012 (2004).

- Massengill, L. W. & Tuinenga, P. W. Single-event transient pulse propagation in digital CMOS. *IEEE Trans. Nucl. Sci.* 55, 2861–2871. https://doi.org/10.1109/TNS.2008.2006749 (2008).

- Ferlet-Cavrois, V., Massengill, L. W. & Gouker, P. Single event transients in digital CMOS—A review. *IEEE Trans. Nucl. Sci.* 60, 1767–1790. https://doi.org/10.1109/TNS.2013.2255624 (2013).

- Dodd, P. E., Shaneyfelt, M. R., Felix, J. A. & Schwank, J. R. Production and propagation of single-event transients in high-speed digital logic ICs. *IEEE Trans. Nucl. Sci.* 51, 3278–3284. https://doi.org/10.1109/TNS.2004.839172 (2004).

- Kim, J., Bang, J., Nakamura, N. & Hosono, H. Ultra-wide bandgap amorphous oxide semiconductors for NBIS-free thin-film transistors. APL Mater. 7, 022501. https://doi.org/10.1063/1.5053762 (2019).

- Sekine, Y. et al. Success in measurement the lowest off-state current of transistor in the world. ECS Trans. 37, 77–88. https://doi. org/10.1149/1.3600726 (2011).

- Shi, J. et al. wide bandgap oxide semiconductors: from materials physics to optoelectronic devices. Adv. Mater. 33, 2006230. https:// doi.org/10.1002/adma.202006230 (2021).

- Wang, C., Hu, Z., He, X., Liao, C. & Zhang, S. One gate diode connected dual-gate a-IGZO TFT driven pixel circuit for active matrix organic light-emitting diode displays. *IEEE Trans. Electron Devices* 63, 3800–3803. https://doi.org/10.1109/TED.2016.25877 18 (2016).

- Lee, J. et al. High-reliability gate driver circuit to prevent ripple voltage. J. Soc. Inf. Display 29, 68–77. https://doi.org/10.1002/jsid. 969 (2020).

- Lin, C. L., Tu, C. D., Chuang, M. C. & Yu, J. S. Design of bidirectional and highly stable integrated hydrogenated amorphous silicon gate driver circuits. J. Display Technol. 7, 10–18. https://doi.org/10.1109/JDT.2010.2085077 (2011).

- Lee, H.-J., Cho, S. H., Abe, K., Lee, M.-J. & Jung, M. Impact of transient currents caused by alternating drain stress in oxide semiconductors. Sci. Rep. 7, 9782–9790. https://doi.org/10.1038/s41598-017-10285-2 (2017).

- Park, J. et al. Self-aligned top-gate amorphous gallium indium zinc oxide thin film transistors. Appl. Phys. Lett. 93, 1–3. https:// doi.org/10.1063/1.2966145 (2008).

- Kim, J. I. et al. Local-degradation-induced threshold voltage shift in turned-OFF amorphous InGaZnO thin film transistors under AC drain bias stress. *IEEE Electron Device Lett.* 36, 579–581. https://doi.org/10.1109/LED.2015.2424966 (2015).

- Wager, J. F., Yeh, B., Hoffman, R. L. & Keszler, D. A. An amorphous oxide semiconductor thin-film transistor route to oxide electronics. *Curr. Opin. Solid State Mater. Sci.* 18, 53–61. https://doi.org/10.1016/j.cossms.2013.07.002 (2014).

- Wang, W. et al. Investigation of light-stimulated α-IGZO based photoelectric transistors for neuromorphic applications. IEEE Trans. Electron Devices 67, 3141–3145. https://doi.org/10.1109/ted.2020.3001492 (2020).

- Kim, S. M., Cho, W. J., Yu, C. G. & Park, J. T. Lifetime prediction of InGaZnO thin film transistor for the application of display device and BEOL-transistors. *Solid-State Electron.* 142, 14–19. https://doi.org/10.1016/j.sse.2018.01.003 (2018).

- Choi, J. Y. & Fossum, J. G. Analysis and control of floating-body bipolar effects in fully depleted submicrometer SO1 MOSFET's. IEEE Trans. Electron Devices 38, 1384–1391. https://doi.org/10.1109/16.81630 (1991).

- Cho, Y. et al. Suppression of the floating-body effect of vertical-cell DRAM with the buried body engineering method. IEEE Trans. Electron Devices 65, 3237–3242. https://doi.org/10.1109/TED.2018.2849106 (2018).

- Chen, J. et al. Extra source implantation for suppression floating-body effect in partially depleted SOI MOSFETs. Nuclear Instrum. Methods Phys. Res. 272, 128–131. https://doi.org/10.1016/j.nimb.2011.01.048 (2012).

- Maeda, S. *et al.* A method for the prediction of hot carrier lifetime in floating SOI NMOSFET's. *IEEE Trans. Electron Devices* 44, 2200–2206. https://doi.org/10.1109/16.644636 (1997).

- 44. Schroder, D. K. Carrier lifetimes in silicon. IEEE Trans. Electron Devices 44, 160–170. https://doi.org/10.1109/16.554806 (1997).

- Seo, J. & Yoo, H. Remote doping effects of indium-gallium-zinc oxide thin-film transistors by silane-based self-assembled monolayers. *Micromachines* 12, 481. https://doi.org/10.3390/mi12050481 (2021).

- Lee, H.-W. & Cho, W.-J. Effects of vacuum rapid thermal annealing on the electrical characteristics of amorphous indium gallium zinc oxide thin films. *AIP Adv.* 8, 015007. https://doi.org/10.1063/1.5009895 (2018).

- Park, Y.-G. et al. Defect engineering for high performance and extremely reliable a-IGZO thin-film transistor in QD-OLED. Adv. Electron. Mater. 8, 2101273. https://doi.org/10.1002/aelm.202101273 (2022).

- Park, J. H. *et al.* Correlation between spin density and V<sub>th</sub> instability of IGZO thin-film transistors. *Curr. Appl. Phys.* 18, 1447–1450. https://doi.org/10.1016/j.cap.2018.08.016 (2018).

#### Acknowledgements

This work was supported by in part by the LG Display Company, in part by the 2023 research fund of Kookmin University in Korea, in part by the National Research Foundation of Korea (NRF) through the Korean Government [Ministry of Science and ICT (MSIT)] under Grant RS-2023-00208661 and NRF-2022R1A2C2092727, in part by the Institute of Information and Communications Technology Planning and Evaluation (IITP) through the Korea Government (MSIT) under Grant 2021-0-01764, and partly by the MOTIE (Ministry of Trade, Industry & Energy (1415187390) and KSRC (Korea Semiconductor Research Consortium) (00231985) support program for the development of the future semiconductor device. The EDA tool was supported in part by the IC Design Education Center (IDEC), Korea, and in part by SILVACO.

#### **Author contributions**

J.P., S.G., S.K. and D.H.K. designed this work and wrote the main part of the manuscript. J.P., W.C., C.I.R., C.K., H.N., and S.K. performed the device characterization, modeling, and TCAD simulation. B.D.A., I.-T.C., P.S.Y., J.U.B., and Y.S.P. contributed to designing and fabricating the IGZO FETs. J.P., S.G., C.I.R., J.U.B., S.K., and D.H.K. discussed the results. The manuscript was written through the contributions of all authors. All authors have approved the final version of the manuscript.

#### **Competing interests**

The authors declare no competing interests.

#### Additional information

**Supplementary Information** The online version contains supplementary material available at https://doi.org/ 10.1038/s41598-024-60288-z.

Correspondence and requests for materials should be addressed to S.K. or D.H.K.

Reprints and permissions information is available at www.nature.com/reprints.

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

© The Author(s) 2024